# ASSP For Power Management Applications (Rechargeable Battery)

# Synchronous Rectification DC/DC Converter IC for Charging Li-ion Battery

# MB39A132

#### DESCRIPTION

MB39A132, which is used for charging Li-ion battery, is a synchronous rectification DC/DC converter IC adopting pulse width modification (PWM). It can control charge voltage and charge current separately and supports the N-ch MOS driver. In addition, MB39A132 is suitable for down-conversion.

MB39A132 has an AC adapter detection comparator, which is independent of the DC/DC converter control block, and can control the source supplying voltage to the system.

MB39A132 supports a wide input voltage range, enables low current consumption in standby mode, and can control the charge voltage and charge current with high precision, which is perfect for the built-in Li-ion battery charger used in devices such as notebook PC.

#### **■ FEATURES**

- Supports 2/3/4-Cell battery pack

- Two built-in constant current control loops

- Built-in AC adapter detection function (ACOK pin)

- Charge voltage setting accuracy: ±0.5% (Ta = +25 °C to +85 °C)

- Charge voltage control setting can be selected without using any external resistor. (4.00 V/Cell, 4.20 V/Cell, 4.35 V/Cell)

Output voltage can also be freely set by using the external resistor.

- Two built-in high-precision current detection amplifiers

- :Input offset voltage:+3 mV

- :Detection accuracy:  $\pm 1$  mV (+INC1, +INC2 = 3 V to VCC)

- Charge current control setting can be selected without using any external resistor. ( $R_S = 20 \text{ m}\Omega$ : 2.85 A) Charge current can also be freely set by using the external resistor.

- Switching frequency can be set by using the external resistor (MB39A132 has a built-in frequency setting capacitor.):100 kHz to 2 MHz

- Built-in off time control function

- In standby mode (Icc =  $6 \mu A$  Typ), only the AC adapter detection function is in operation.

etc.

- Built-in output stage for N-ch MOS FET synchronous rectification

- Built-in charge stop function at low VCC pin voltage

- Built-in soft-start function whose setting time can be adjusted

- Equipped with the function enabling the independent operation of the AC adapter current detection amplifier

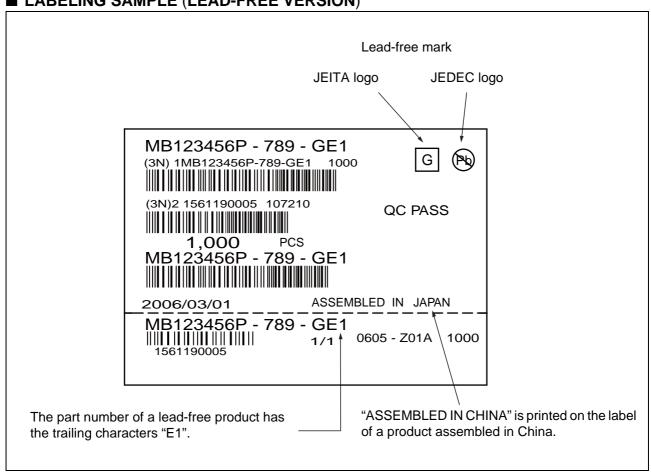

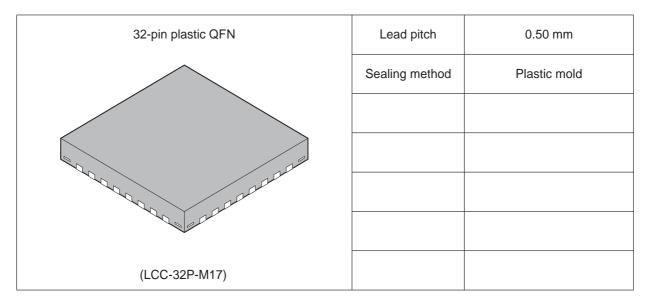

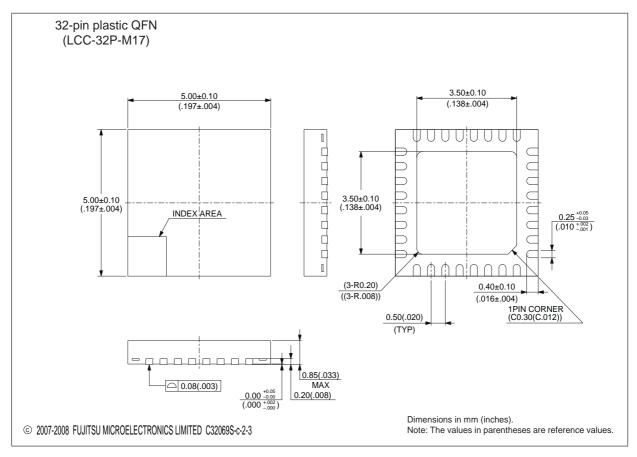

- Package: QFN-32

#### **■** APPLICATIONS

- Internal charger used in notebook PC

- Handy terminal device

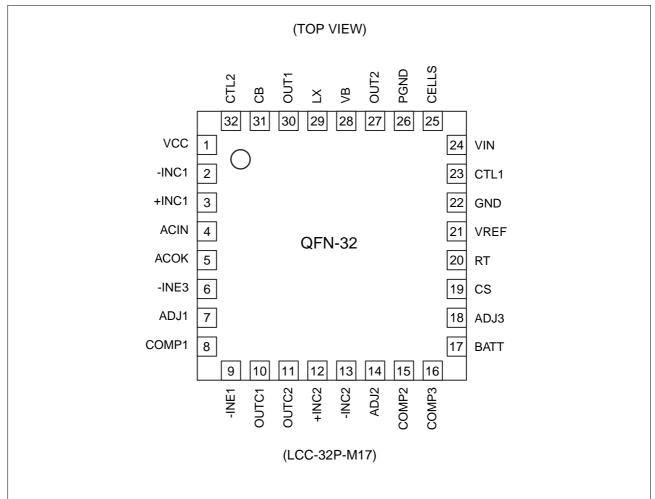

### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTIONS**

| Pin No. | Pin Name | I/O | Description                                                                                                                                                                                                                                                                   |  |  |  |

|---------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | VCC      | _   | Power supply pin for reference power and control circuit (Battery side).                                                                                                                                                                                                      |  |  |  |

| 2       | -INC1    |     | Current detection amplifier (Current Amp1) inverted input pin.                                                                                                                                                                                                                |  |  |  |

| 3       | +INC1    | I   | Current detection amplifier (Current Amp1) non-inverted input pin.                                                                                                                                                                                                            |  |  |  |

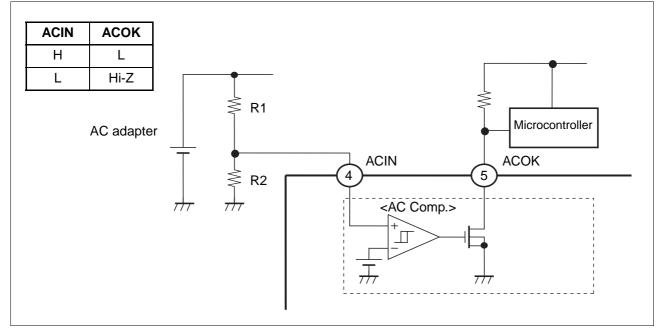

| 4       | ACIN     | I   | AC adapter voltage detection block (AC Comp.) input pin.                                                                                                                                                                                                                      |  |  |  |

| 5       | ACOK     | 0   | AC adapter voltage detection block (AC Comp.) output pin.<br>ACOK = Lo-Z when ACIN = H, ACOK = Hi-Z when ACIN = L                                                                                                                                                             |  |  |  |

| 6       | -INE3    | ı   | Error amplifier (Error Amp3) inverted input pin.                                                                                                                                                                                                                              |  |  |  |

| 7       | ADJ1     | ı   | Error amplifier (Error Amp1) non-inverted input pin.                                                                                                                                                                                                                          |  |  |  |

| 8       | COMP1    | 0   | Error amplifier (Error Amp1) output pin.                                                                                                                                                                                                                                      |  |  |  |

| 9       | -INE1    |     | Error amplifier (Error Amp1) inverted input pin.                                                                                                                                                                                                                              |  |  |  |

| 10      | OUTC1    | 0   | Current detection amplifier (Current Amp1) output pin.                                                                                                                                                                                                                        |  |  |  |

| 11      | OUTC2    | 0   | Current detection amplifier (Current Amp2) output pin.                                                                                                                                                                                                                        |  |  |  |

| 12      | +INC2    |     | Current detection amplifier (Current Amp2) non-inverted input pin.                                                                                                                                                                                                            |  |  |  |

| 13      | -INC2    |     | Current detection amplifier (Current Amp2) inverted input pin.                                                                                                                                                                                                                |  |  |  |

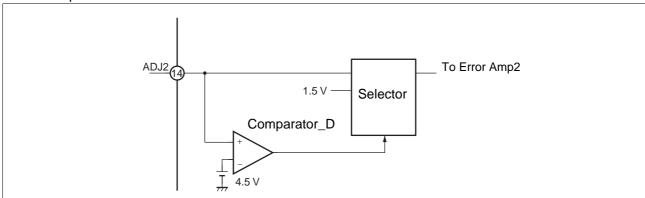

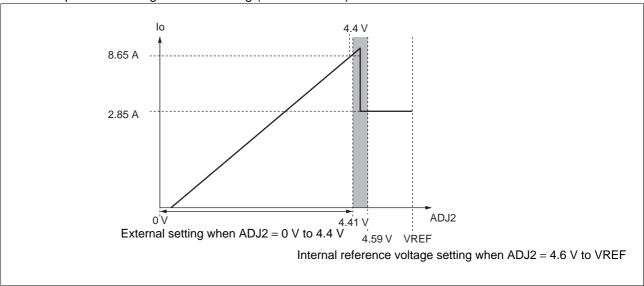

| 14      | ADJ2     | I   | Input pin for the charge current control block.  ADJ2 pin "GND to 4.4 V" :Charge current control block output =  ADJ2 pin voltage  ADJ2 pin "4.6 V to VREF" :Charge current control block output = 1.5 V                                                                      |  |  |  |

| 15      | COMP2    | 0   | Error amplifier (Error Amp2) output pin.                                                                                                                                                                                                                                      |  |  |  |

| 16      | COMP3    | 0   | Error amplifier (Error Amp3) output pin.                                                                                                                                                                                                                                      |  |  |  |

| 17      | BATT     | l   | Charge voltage control block battery voltage input pin.                                                                                                                                                                                                                       |  |  |  |

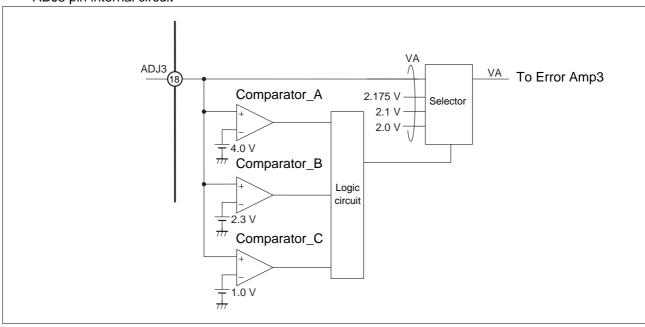

| 18      | ADJ3     | I   | Charge voltage control block setting input pin.  ADJ3 pin "GND" :Charge voltage 4.00 V/Cell  ADJ3 pin "1.1 V to 2.2 V" :Charge voltage 2 × ADJ3 pin voltage/Cell  ADJ3 pin "2.4 V to 3.9 V" :Charge voltage 4.35 V/Cell  ADJ3 pin "4.1 V to VREF" :Charge voltage 4.20 V/Cell |  |  |  |

| 19      | CS       | _   | Soft-start capacitor connection pin.                                                                                                                                                                                                                                          |  |  |  |

| 20      | RT       |     | Triangular wave oscillation frequency setting resistor connection pin.                                                                                                                                                                                                        |  |  |  |

| 21      | VREF     | 0   | Reference voltage output pin.                                                                                                                                                                                                                                                 |  |  |  |

| 22      | GND      | _   | Ground pin.                                                                                                                                                                                                                                                                   |  |  |  |

| 23      | CTL1     | I   | Power supply control pin. When the CTL1 pin is set to "H" level, the DC/DC converter becomes operable. When the CTL1 pin is set to "L" level, the DC/DC converter becomes stand-by.                                                                                           |  |  |  |

| 24      | VIN      |     | Power supply pin for ACOK function and Current Amp1(AC adapter side).                                                                                                                                                                                                         |  |  |  |

| 25      | CELLS    | I   | Charge voltage setting switch pin (2/3/4-Cell). CELLS = VREF: 4 Cells, CELLS = OPEN: 3 Cells, CELLS = GND: 2 Cells                                                                                                                                                            |  |  |  |

| 26      | PGND     | _   | Ground pin.                                                                                                                                                                                                                                                                   |  |  |  |

| 27      | OUT2     | 0   | External low-side FET gate drive pin.                                                                                                                                                                                                                                         |  |  |  |

| 28      | VB       | 0   | FET drive circuit power supply pin.                                                                                                                                                                                                                                           |  |  |  |

| 29      | LX       | _   | External high-side FET source connection pin.                                                                                                                                                                                                                                 |  |  |  |

| 30      | OUT1     | 0   | External high-side FET gate drive pin.                                                                                                                                                                                                                                        |  |  |  |

| Pin No. | Pin Name | I/O | Description                                                                                                                                                                                          |

|---------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | СВ       | _   | Boot strap capacitor connection pin. The capacitor is connected between the CB pin and the LX pin.                                                                                                   |

| 32      | CTL2     | I   | Power supply control pin for Current Amp1. When the CTL1 pin is set to "H" level, the DC/DC converter becomes operable. When the CTL1 pin is set to "L" level, the DC/DC converter becomes stand-by. |

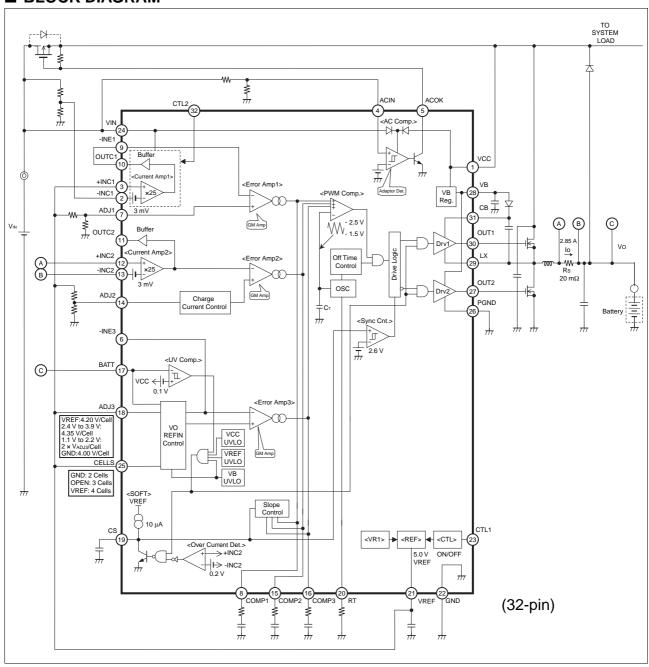

#### **■ BLOCK DIAGRAM**

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                    | Cumbal           | Condition                    | Ra    | ting         | Unit |

|------------------------------|------------------|------------------------------|-------|--------------|------|

| Parameter                    | Symbol           | Condition                    | Min   | Max          | Unit |

| Dower supply voltage         | Vvcc             | VCC pin                      | - 0.3 | + 27         | V    |

| Power supply voltage         | Vvin             | VIN pin                      | - 0.3 | + 27         | V    |

| CB pin input voltage         | Vсв              | CB pin                       | - 0.3 | + 32         | V    |

| CTL1, CTL2 pin input voltage | Vctl             | CTL1, CTL2 pins              | - 0.3 | + 27         | V    |

|                              | VINC             | -INC1, +INC1 pins            | - 0.3 | + 27         | V    |

| Input voltage                | VINC             | -INC2, +INC2, BATT pins      | - 0.3 | + 20         | V    |

| Input voltage                | V <sub>ADJ</sub> | ADJ1, ADJ2, ADJ3, CELLS pins | - 0.3 | VVREF + 0.3  | V    |

|                              | VINE             | -INE1, -INE3 pins            | - 0.3 | VVREF + 0.3  | V    |

| ACIN input voltage           | Vacin            | ACIN pin                     | - 0.3 | Vvin         | V    |

| ACOK pin output voltage      | Vacok            | ACOK pin                     | - 0.3 | + 27         | V    |

| Output current               | Іоит             | OUT1, OUT2 pins              | - 60  | + 60         | mA   |

|                              |                  | Ta < + 25 °C                 | _     | 4400*1,*2,*3 | mW   |

| Davis a dia sin atia a       | PD               | 1a \( + \( \)   C            | _     | 1900*1,*2,*4 | mW   |

| Power dissipation            | FD               | To _ + 95 °C                 | _     | 1760*1,*2,*3 | mW   |

|                              |                  | Ta = +85 °C                  | _     | 760*1,*2,*4  | mW   |

| Storage temperature          | Тѕтс             | _                            | - 55  | + 125        | °C   |

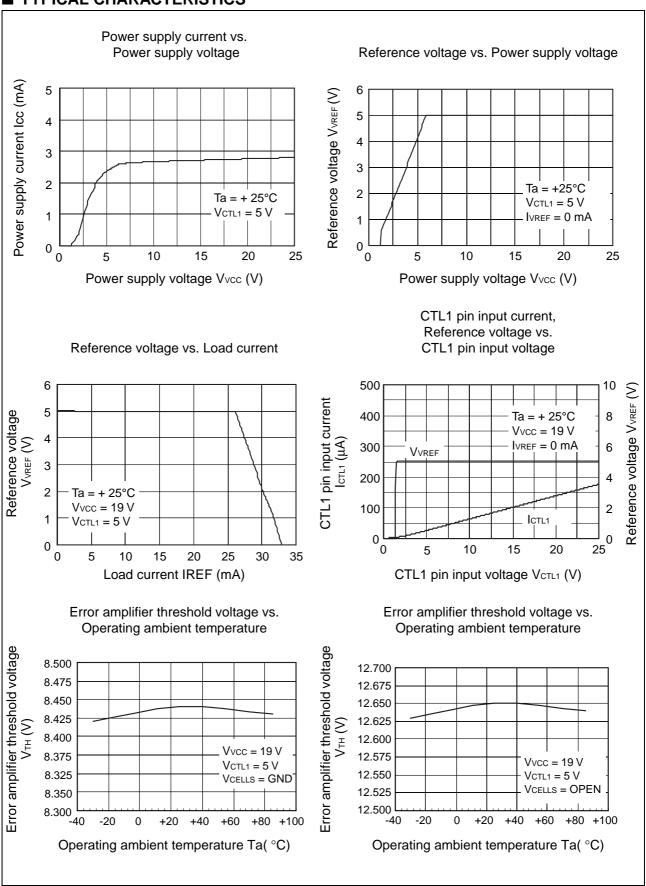

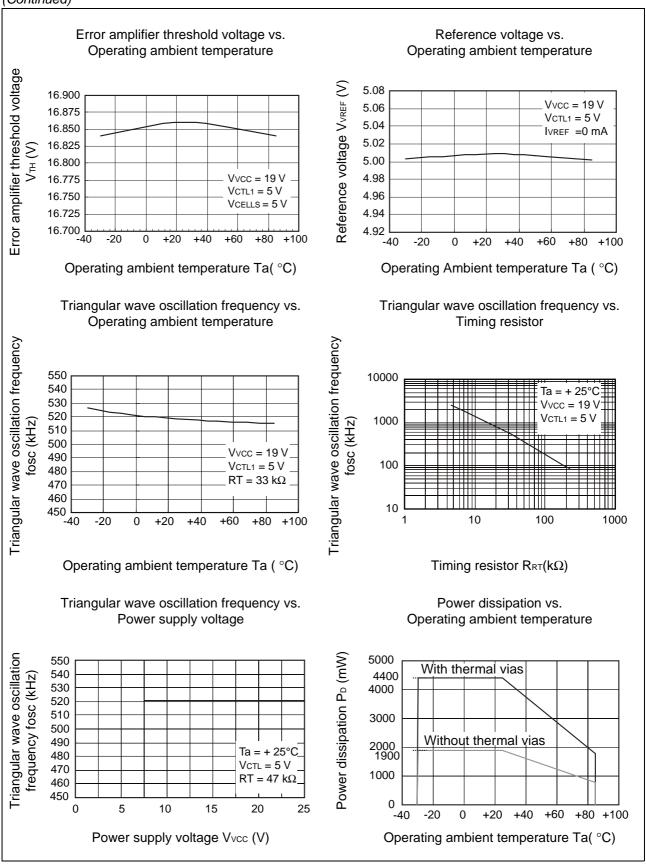

<sup>\*1 :</sup> See the diagram of "■ TYPICAL CHARACTERISTICS • Power Dissipation vs. Operating Ambient Temperature", for the package power dissipation of Ta from + 25 °C to + 85 °C.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

<sup>\*2:</sup> When the IC is mounted on a 10x10 cm two-layer square epoxy board.

<sup>\*3:</sup> IC is mounted on a two-layer epoxy board, which has thermal vias, and the IC's thermal pad is connected to the epoxy board.

<sup>\*4:</sup> IC is mounted on a two-layer epoxy board, which has no thermal vias, and the IC's thermal pad is connected to the epoxy board.

### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                          | Symbol      | Condition                                                    | Min        | Тур  | Max                     | Unit |

|------------------------------------|-------------|--------------------------------------------------------------|------------|------|-------------------------|------|

| Davisas averalis valta as          | Vvcc        | VCC pin                                                      | 8          | _    | 25                      | V    |

| Power supply voltage               | Vvin        | VIN pin                                                      | 8          | _    | 25                      | V    |

| CB pin input voltage               | Vсв         | CB pin                                                       | _          |      | 30                      | V    |

| Reference voltage output current   | Ivref       | _                                                            | - 1        |      | 0                       | mA   |

| Bias output current                | Ivв         | _                                                            | <b>– 1</b> | _    | 0                       | mA   |

|                                    | VINC        | -INC1, +INC1 pins                                            | 0          | _    | Vvcc                    | V    |

|                                    | VINC        | -INC2, +INC2, BATT pins                                      | 0          | _    | 19                      | V    |

|                                    |             | ADJ1 pin                                                     | 0          | _    | V <sub>VREF</sub> – 1.5 | V    |

|                                    |             | ADJ2 pin                                                     | 4.6        | _    | Vvref                   | >    |

| Input voltage                      |             | (when using the internal reference voltage)                  | 0          | _    | 0.2                     | V    |

|                                    | Vadj        | ADJ2 pin<br>(external voltage setting)                       | 0.4        | _    | 4.4                     | V    |

|                                    |             | ADJ3 pin                                                     | 4.1        | _    | $V_{VREF}$              | V    |

|                                    |             | (when using the internal                                     | 2.4        | _    | 3.9                     | V    |

|                                    |             | reference voltage)                                           | 0          | _    | 0.9                     | V    |

|                                    |             | ADJ3 pin (external voltage setting)                          | 1.1        |      | 2.2                     | V    |

|                                    |             | CELLS pin                                                    | 0          | _    | Vvref                   | V    |

|                                    | VINE        | -INE1, -INE3 pins                                            | 0          | _    | Vvref                   | V    |

| ACIN pin input voltage             | Vacin       | _                                                            | 0          | _    | VVREF                   | V    |

| ACOK pin output voltage            | Vасок       | _                                                            | 0          |      | 25                      | V    |

| ACOK pin output current            | Іасок       | _                                                            | 0          |      | 1                       | mA   |

| CTL1, CTL2 pin input voltage       | Vctl        | _                                                            | 0          |      | 25                      | V    |

|                                    |             | OUT1, OUT2 pins                                              | - 45       | _    | + 45                    | mA   |

| Output current                     | Іоит        | OUT1, OUT2 pins<br>Duty $\leq$ 5% (t = 1/fosc $\times$ Duty) | - 1200     |      | + 1200                  | mA   |

| Switching frequency                | fosc        | _                                                            | 100        | 500  | 2000                    | kHz  |

| Timing resistor                    | <b>R</b> RT | RT pin                                                       | 8.2        | 33   | 180                     | kΩ   |

| Soft-start capacitor               | Ccs         | CS pin                                                       | _          | 0.22 | _                       | μF   |

| CB pin capacitor                   | Ссв         | _                                                            | _          | 0.1  | _                       | μF   |

| Bias output capacitor              | Сув         | VB pin                                                       | _          | 1.0  | _                       | μF   |

| Reference voltage output capacitor | Cref        | VREF pin                                                     | _          | 0.1  | 1.0                     | μF   |

(Continued)

7

#### (Continued)

| Parameter                     | Symbol   | Condition |      | Unit |      |       |

|-------------------------------|----------|-----------|------|------|------|-------|

| raiailletei                   | Syllibol | Condition | Min  | Тур  | Max  | Oiiit |

| Operating ambient temperature | Та       | <u> </u>  | - 30 | + 25 | + 85 | °C    |

8

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure. No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

### **■ ELECTRICAL CHARACTERISTICS**

(Ta = +25 °C, VCC pin = 19 V, VB pin = 0 mA, VREF pin = 0 mA)

| Para                                     | Parameter                             |                  | Pin | Condition                                                         |       | Value |       | Unit |

|------------------------------------------|---------------------------------------|------------------|-----|-------------------------------------------------------------------|-------|-------|-------|------|

| Parai                                    | neter                                 | Symbol           | No. | Condition                                                         | Min   | Тур   | Max   | Onit |

|                                          | Threshold                             | Vvref1           | 21  | _                                                                 | 4.963 | 5.000 | 5.037 | V    |

|                                          | voltage                               | Vvref2           | 21  | $Ta = -10 {}^{\circ}\text{C} \text{ to } + 85 {}^{\circ}\text{C}$ | 4.950 | 5.000 | 5.050 | V    |

| Reference                                | Input stability                       | VREF             | 21  | VCC pin = 8 V to 25 V                                             | _     | 1     | 10    | mV   |

| Voltage Block<br>[REF]                   | Load stability                        | VREF             | 21  | VREF pin = 0 mA to<br>- 1mA                                       |       | 1     | 10    | mV   |

|                                          | Short-circuit output current          | los              | 21  | VREF pin = 1 V                                                    | - 70  | - 35  | - 17  | mA   |

| Triangular<br>Wave                       | Oscillation frequency                 | fosc             | 30  | RT pin = 33 k $\Omega$                                            | 450   | 500   | 550   | kHz  |

| Oscillator<br>Block<br>[OSC]             | Frequency<br>temperature<br>variation | df/fdT           | 30  | $Ta = -30  ^{\circ}C \text{ to } + 85  ^{\circ}C$                 | _     | 1*    | _     | %    |

|                                          | Input offset voltage                  | Vio              | 7   | COMP1 pin = 2 V                                                   | _     | 1*    | 5     | mV   |

| Error Amplifier<br>Block<br>[Error Amp1] | Input bias current                    | ladj1            | 7   | ADJ1 pin = 0 V                                                    | - 100 |       |       | nA   |

| [,                                       | Transconduc-<br>tance                 | Gm               | 8   | _                                                                 |       | 20*   |       | μΑ/V |

| Error Amplifier<br>Block                 | Threshold voltage                     | V <sub>TH1</sub> | 14  | ADJ2 pin =<br>VREF pin                                            |       | 1.5*  |       | V    |

| [Error Amp2]                             | Transconduc-<br>tance                 | Gm               | 15  | _                                                                 | _     | 20*   |       | μΑ/V |

(Ta = +25 °C, VCC pin = 19 V, VB pin = 0 mA, VREF pin = 0 mA)

| Poron                    | notor                 | Symbol           | Pin | Condition                                                                                                     |       | Value |       | Unit |

|--------------------------|-----------------------|------------------|-----|---------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Paran                    | Parameter             |                  | No. | Condition                                                                                                     | Min   | Тур   | Max   | Unit |

|                          |                       | V <sub>ТН1</sub> | 17  | COMP3 pin = 2 V,<br>Ta = +25 °C to +85 °C<br>ADJ3 pin = CELLS pin =<br>VREF pin                               | - 0.5 | 0     | + 0.5 | %    |

|                          |                       | V <sub>TH2</sub> | 17  | COMP3 = 2 V,<br>Ta = $-10$ °C to $+85$ °C<br>ADJ3 pin = CELLS pin =<br>VREF pin                               | - 0.7 | 0     | + 0.5 | %    |

|                          | Threshold             | Vтнз             | 17  | COMP3 = 2 V,<br>Ta = $+25$ °C to $+85$ °C<br>$2.4$ V $\leq$ ADJ3 pin $\leq$ 3.9 V<br>CELLS pin = VREF pin     | - 0.5 | 0     | + 0.5 | %    |

| Error Amplifier<br>Block | Block                 | V <sub>TH4</sub> | 17  | COMP3 pin = 2 V,<br>Ta = $-10$ °C to $+85$ °C<br>$2.4$ V $\leq$ ADJ3 pin $\leq$ 3.9 V<br>CELLS pin = VREF pin | - 0.7 | 0     | + 0.5 | %    |

| [Error Amp3]             |                       | Vтн5             | 17  | COMP3 pin = 2 V,<br>Ta = $+25$ °C to $+85$ °C<br>ADJ3 = GND pin,<br>CELLS pin = VREF pin                      | - 0.5 | 0     | + 0.5 | %    |

|                          |                       | <b>V</b> тн6     | 17  | COMP3 pin = 2 V,<br>Ta = $-10$ °C to $+85$ °C<br>ADJ3 pin = GND pin,<br>CELLS pin = VREF pin                  | - 0.7 | 0     | + 0.5 | %    |

|                          | Input current         | Іваттн           | 17  | $2.4 \text{ V} \le \text{ADJ3} \le 3.9 \text{ V}$<br>CELLS pin = VREF pin, BATT pin = 16.8 V                  | l     | 34    | 60    | μΑ   |

|                          |                       | <b>I</b> BATTL   | 17  | VCC pin = 0 V,<br>BATT pin = 16.8 V                                                                           |       | 0     | 1     | μА   |

|                          | Transcon-<br>ductance | Gm               | 16  | _                                                                                                             |       | 280*  |       | μΑ/V |

$(Ta = + 25 \degree C, VCC pin = 19 V, VB pin = 0 mA, VREF pin = 0 mA)$

| Doron                                              | 20404                                 | Sym-               | Pin   | Condition                                                        | Value |       |            | Unit |

|----------------------------------------------------|---------------------------------------|--------------------|-------|------------------------------------------------------------------|-------|-------|------------|------|

| Paran                                              | leter                                 | bol                | No.   | Condition                                                        | Min   | Тур   | Max        | Unit |

|                                                    |                                       | I+INCH1            | 3     | +INC1 pin = 3 V to VCC pin,<br>$\Delta$ Vin = -100 mV            |       | 20    | 30         | μА   |

|                                                    |                                       | I+INCH2            | 12    | +INC2 pin = 3 V to VCC pin,<br>$\Delta$ Vin = -100 mV            |       | 30    | 45         | μА   |

|                                                    | Input current                         | I-inch             | 2,13  | $\begin{array}{llllllllllllllllllllllllllllllllllll$             |       | 0.1   | 0.2        | μА   |

|                                                    |                                       | I+INCL             | 3,12  | +INC1 pin = +INC2 pin = 0.1 V, $\Delta$ Vin = -100 mV            | - 240 | - 160 | 1          | μА   |

|                                                    |                                       | <b>I-</b> INCL     | 2,13  | - INC1 pin = - INC2 pin = 0.1 V,<br>$\Delta Vin = - 100 mV$      | - 270 | - 180 | _          | μА   |

|                                                    | Input offset                          | $V_{OFF1}$         | 10,11 | +INC1 pin = +INC2 pin = 3 V to VCC pin                           | 2     | 3     | 4          | mV   |

| Current<br>Detection                               | voltage                               | V <sub>OFF2</sub>  | 10,11 | +INC1 pin = +INC2 pin = 0 V to 3 V                               | 1     | 3     | 5          | mV   |

| Amplifier Block<br>[Current Amp1,<br>Current Amp2] | Common<br>mode input<br>voltage range | Vсм                | 10,11 | _                                                                | 0     | _     | Vvcc       | V    |

|                                                    | Voltage gain                          | Av                 | 10,11 | +INC1 pin = +INC2 pin = 3 V to VCC pin, $\Delta$ Vin = $-100$ mV | 24.5  | 25.0  | 25.5       | V/V  |

|                                                    | Frequency bandwidth                   | BW                 | 10,11 | $A_V = 0 dB$                                                     | _     | 2*    | _          | MHz  |

|                                                    | Output                                | Vоитсн             | 10,11 | _                                                                | 4.7   | 4.9   |            | V    |

|                                                    | voltage                               | Voutcl             | 10,11 | +INC1 pin = +INC2 pin = 3 V to VCC pin                           | 50    | 75    | 100        | mV   |

|                                                    | Output source current                 | Isource            | 10,11 | OUTC1 pin =<br>OUTC2 pin = 2 V                                   |       | - 2   | <b>– 1</b> | mA   |

|                                                    | Output sink current                   | Isink              | 10,11 | OUTC1 pin =<br>OUTC2 pin = 2 V                                   | 25    | 50    |            | μА   |

|                                                    | OUTC1 pin<br>Output<br>voltage        | Voutc <sub>1</sub> | 10    | VIN pin = 0 V                                                    |       | 0     |            | V    |

| PWM                                                |                                       | VTL                | 30    | Duty cycle = 0 %                                                 | 1.4   | 1.5   | _          | V    |

| Comparator<br>Block<br>[PWM Comp.]                 |                                       | Vтн                | 30    | Duty cycle = 100 %                                               |       | 2.5   | 2.6        | V    |

| Output Block                                       | Output                                | Rон                | 27,30 | OUT1,OUT2 pin = $-45 \text{ mA}$                                 |       | 4     | 7          | Ω    |

| [OUT]                                              | ON resistance                         | Rol                | 27,30 | OUT1,OUT2 pin = $+45 \text{ mA}$                                 |       | 1     | 3.5        | Ω    |

(Ta = +25 °C, VCC pin = 19 V, VB pin = 0 mA, VREF pin = 0 mA)

| _                                                         |                                            | •                | Pin Condition |                             | Value |       |       | - U IIIA) |

|-----------------------------------------------------------|--------------------------------------------|------------------|---------------|-----------------------------|-------|-------|-------|-----------|

| Paran                                                     | neter                                      | Symbol           | No.           | Condition                   | Min   | Тур   | Max   | Unit      |

|                                                           | ON condition                               | VON              | 23,32         | IC operation mode           | 2     | _     | 25    | V         |

| Control Block                                             | OFF condition                              | VOFF             | 23,32         | IC standby mode             | 0     | _     | 0.8   | V         |

| [CTL1,CTL2]                                               | Input current                              | Істін            | 23,32         | CTL1, CTL2 pin = 5 V        | _     | 25    | 40    | μΑ        |

|                                                           | Input current                              | ICTLL            | 23,32         | CTL1, CTL2 pin = 0 V        |       | 0     | 1     | μΑ        |

| Bias Voltage                                              | Output voltage                             | VB               | 28            | _                           | 4.9   | 5.0   | 5.1   | V         |

| Block<br>[VB]                                             | Load stability                             | Load             | 28            | VB pin = 0 mA to<br>- 10 mA |       | 10    | 50    | mV        |

| Synchronous                                               | CS threshold                               | $V_{TLH}$        | 19            |                             | 2.55  | 2.60  | 2.65  | V         |

| Rectification                                             | voltage                                    | $V_{THL}$        | 19            | _                           | 2.5   | 2.55  | 2.60  | V         |

| Control Block<br>[Synchronous<br>Cnt.]                    | Hysteresis width                           | Vн               | 19            | _                           | _     | 0.05* | _     | ٧         |

|                                                           | Threshold                                  | VTLH             | 1             | VCC pin                     | _     | 7.5   | 7.9   | V         |

|                                                           | voltage                                    | VTHL             | 1             | VCC pin                     | 7.0   | 7.4   |       | V         |

|                                                           | Hysteresis width                           | Vн               | 1             | VCC pin                     |       | 0.1   | _     | V         |

| Under Voltage                                             | Threshold                                  | VTLH             | 28            | VB pin                      | 3.8   | 4.0   | 4.2   | V         |

| Lockout<br>Protection                                     | voltage                                    | VTHL             | 28            | VB pin                      | 3.1   | 3.3   | 3.5   | V         |

| Circuit Block                                             | Hysteresis width                           | Vн               | 28            | VB pin                      |       | 0.7   | _     | V         |

|                                                           | Threshold                                  | VTLH             | 21            | VREF pin                    | 2.6   | 2.8   | 3.0   | V         |

|                                                           | voltage                                    | VTHL             | 21            | VREF pin                    | 2.4   | 2.6   | 2.8   | V         |

|                                                           | Hysteresis width                           | Vн               | 21            | VREF pin                    |       | 0.2   | _     | V         |

| Over Current<br>Detection Block<br>[Over Current<br>Det.] | Output voltage                             | Vн               | 12            | -INC2 pin = 12.6 V          | 12.75 | 12.80 | 12.85 | V         |

| Under Input                                               | Threshold                                  | $V_{TLH}$        | 1             | BATT pin = 12.6 V           | 12.6  | 12.8  | 13.0  | V         |

| Voltage                                                   | voltage                                    | V <sub>THL</sub> | 1             | BATT pin = 12.6 V           | 12.5  | 12.7  | 12.9  | V         |

| Detection Block [UV Comp.]                                | Hysteresis width                           | Vн               | 1             | BATT pin = 12.6 V           |       | 0.1   |       | ٧         |

|                                                           | Threshold                                  | $V_{TLH}$        | 4             | _                           | 1.237 | 1.250 | 1.263 | V         |

|                                                           | voltage                                    | $V_{THL}$        | 4             | _                           | 1.227 | 1.240 | 1.253 | V         |

|                                                           | Hysteresis width                           | Vн               | 4             | _                           |       | 10    |       | mV        |

| AC Adapter                                                | Input current                              | I-INCL           | 4             | _                           | _     | _     | 200   | nA        |

| Voltage<br>Detection Block<br>[AC Comp.]                  | ACOK<br>pin<br>output leak<br>current      | Ileak            | 5             | ACOK pin = 25 V             | _     | 0     | 1     | μΑ        |

|                                                           | ACOK<br>pin<br>output "L"<br>Level voltage | Vacokl           | 5             | ACOK pin = 1 mA             |       | 0.9   | 1.1   | V         |

(Ta = +25 °C, VCC pin = 19 V, VB pin = 0 mA, VREF pin = 0 mA)

| Barrarr                         |                      | Comple of        | Pin  | O a w distinge                                                                             |                         | Value      |       | I Init |

|---------------------------------|----------------------|------------------|------|--------------------------------------------------------------------------------------------|-------------------------|------------|-------|--------|

| Paran                           | neter                | Symbol           | No.  | Condition                                                                                  | Min                     | Тур        | Max   | Unit   |

|                                 |                      | Vтнн             | 18   | At 4.2 V/Cell                                                                              | 3.91                    | 4.00       | 4.09  | V      |

|                                 | Threshold voltage    | V <sub>ТНМ</sub> | 18   | At 4.35 V/Cell                                                                             | 2.21                    | 2.30       | 2.39  | V      |

|                                 | Vollago              | V <sub>THL</sub> | 18   | At 4.0 V/Cell                                                                              | 0.91                    | 1.00       | 1.09  | V      |

| Charge Voltage                  | Input current        | Iın              | 18   | ADJ3 pin                                                                                   |                         | 0          | 1     | μА     |

| Control Block<br>[VO REFIN      |                      | Vн               | 25   | At 4Cells                                                                                  | V <sub>VREF</sub> – 0.4 |            | VVREF | ٧      |

| Control]                        | Input voltage        | Vм               | 25   | At 3Cells                                                                                  | 2.4                     |            | 2.6   | V      |

|                                 |                      | VL               | 25   | At 2Cells                                                                                  | 0                       |            | 0.3   | V      |

|                                 | Input current        | IINL             | 25   | CELLS pin = 0 V                                                                            | - 8.3                   | <b>- 5</b> |       | μΑ     |

|                                 | Imput current        | Inh              | 25   | CELLS pin = VREF pin                                                                       |                         | 5          | 8.3   | μΑ     |

| Charge Current<br>Control Block | Threshold voltage    | V <sub>тн</sub>  | 14   | _                                                                                          | 4.41                    | 4.5        | 4.59  | V      |

| [Charge<br>Current<br>Control]  | Input current        | lın              | 14   | ADJ2 pin                                                                                   | _                       | 0          | 1     | μА     |

| Soft-start Block<br>[SOFT]      | Charge current       | Ics              | 19   | _                                                                                          | - 14                    | - 10       | - 6   | μΑ     |

|                                 |                      | IVINL            | 24   | VIN pin = 19 V,<br>ACIN pin = 0 V                                                          | _                       | 0          | 1     | μА     |

|                                 | Standby current      | lins             | 24   | VCC pin = 0 V,<br>CTL1, CTL2 pin = 0 V,<br>ACIN pin = 5 V,<br>VIN pin = 19 V               | _                       | 6          | 10    | μА     |

|                                 |                      | Iccs             | 1    | VIN pin = 0 V,<br>CTL1, CTL2 pin = 0 V,<br>ACIN pin = 0 V,<br>VCC pin = 19 V               | _                       | 0          | 1     | μΑ     |

| General                         |                      | lin              | 24   | VIN pin = 19 V,<br>VCC pin = 0 V,<br>ACIN pin = 5 V,<br>CTL1 pin = 0 V,<br>CTL2 pin = 5 V  | _                       | 300        | 450   | μΑ     |

|                                 | Power supply current | Icc              | 1    | VIN pin = 0 V,<br>VCC pin = 19 V,<br>ACIN pin = 0 V,<br>CTL1 pin = 5 V,<br>CTL2 pin = 0 V  | _                       | 2.4        | 3.6   | mA     |

|                                 |                      | lincc            | 1,24 | VIN pin = 19 V,<br>VCC pin = 19 V,<br>ACIN pin = 5 V,<br>CTL1 pin = 5 V,<br>CTL2 pin = 5 V | _                       | 2.7        | 4.1   | mA     |

<sup>\*:</sup> This value is not be specified. This should be used as a reference to support designing the circuits.

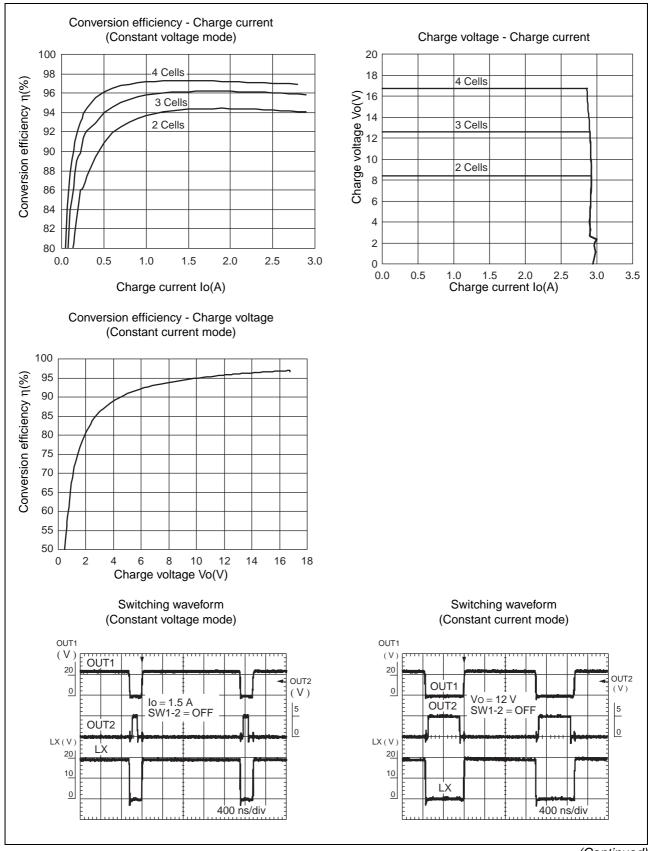

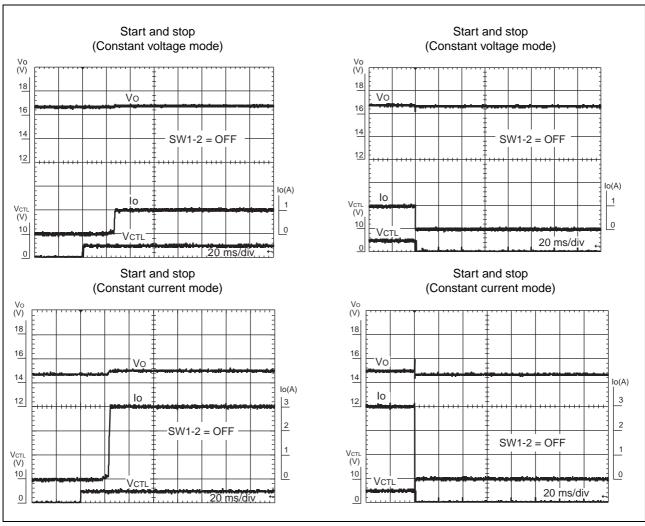

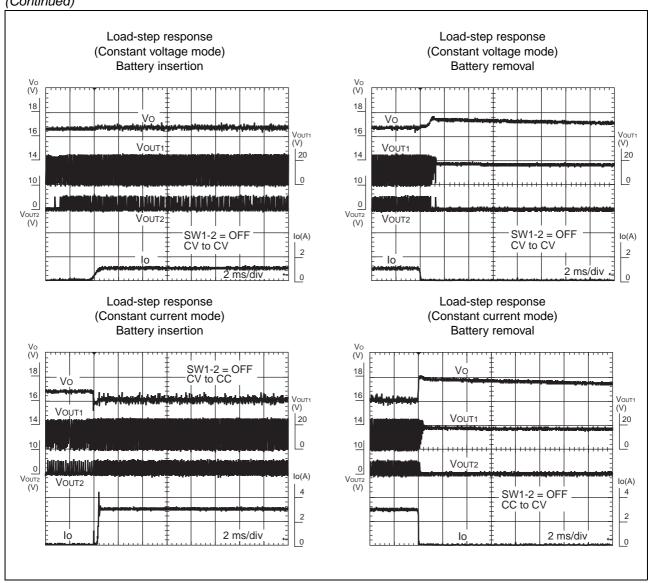

#### **■ TYPICAL CHARACTERISTICS**

#### **■ FUNCTIONAL DESCRIPTION**

MB39A132 is an N-ch MOS driver-supported DC/DC converter which uses pulse width modulation (PWM) for charging Li-ion battery and controls the charge voltage and current when charging the battery. To stabilize the power supplied from a battery or an adapter to a system, this DC/DC converter has a battery charging control function and an AC adapter voltage detection function.

When MB39A132 controls charge voltage (constant voltage mode), it can freely set the charge voltage with the voltage input to the ADJ3 pin (pin 18) and the CELLS pin (pin 25). It compares the BATT pin (pin 17) voltage and the internal reference voltage with the error amplifier (Error Amp3), outputs PWM control signals and then outputs the charge voltage freely set by the IC.

When MB39A132 controls charge current (constant current mode), it amplifies the voltage drop occurring on both ends of the charge current sense resistor (Rs) by 25 times with the current detection amplifier (Current Amp2), and then outputs the amplified voltage to the OUTC2 pin (pin 11). It compares the output voltage of the current detection amplifier (Current Amp2) and the voltage set in the ADJ2 pin (pin 14) with the error amplifier (Error Amp2), and then outputs PWM control signals for executing constant-current charge.

When MB95A132 controls AC adapter power, in the case of an output voltage drop in the AC adapter, the converter amplifies the voltage difference between the voltage applied to the -INC1 pin (pin 2) that has dropped and the +INC1 pin (pin 3) voltage (V<sub>VREF</sub>) by 25 times with the current detection amplifier (Error Amp1), and then outputs the amplified voltage value to the OUTC1 pin (pin 10). It compares the output voltage of the current detection amplifier (Current Amp1) to the ADJ1 pin (pin 7) voltage using the error amplifier (Error Amp1) to output PWM control signals for controlling the charge current so that the AC adapter power can be kept constant.

The triangular wave voltage generated by the triangular wave oscillator is compared with the output voltage of one of the three error amplifiers (Error Amp1, Error Amp2 and Error Amp3) that has the lowest potential. The main FET is turned on during the period when the triangular wave voltage is lower than the error amplifier output voltage.

In addition, the AC Comp. detects installation/removal of the AC adapter and its information is output through the ACOK pin (pin 5).

#### 1. Blocks of DC/DC Converter

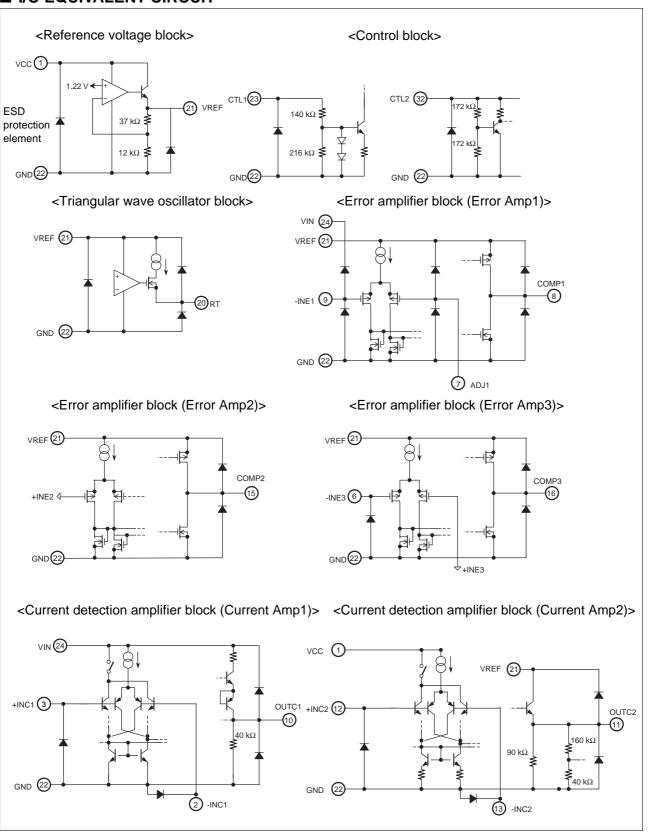

#### (1) Reference voltage block (REF)

The reference voltage circuit uses the voltage supplied from the VCC pin (pin 1) to generate stable voltage (Typ. 5.0 V) that has undergone temperature compensation. The generated voltage is used as the reference power supply for the internal circuitry of the IC.

This block can output load current of up to 1 mA from the reference voltage VREF pin (pin 21).

#### (2) Triangular wave oscillator block (OSC)

The triangular wave oscillator builds the capacitor for frequency setting into, and generates the triangular wave oscillation waveform by connecting the frequency setting resistor with the RT pin (pin 20).

The triangular wave is input to the PWM comparator on the IC.

Triangular wave oscillation frequency: fosc

fosc (kHz)  $\Rightarrow$  17000/RT (k $\Omega$ )

#### (3) Error amplifier block (Error Amp1)

This amplifier detects the output signal from the current detection amplifier (Current Amp1) and outputs a PWM control signal.

In addition, a stable phase compensation can be made available to the system by connecting the resistor and the capacitor to the COMP1 pin (pin 8).

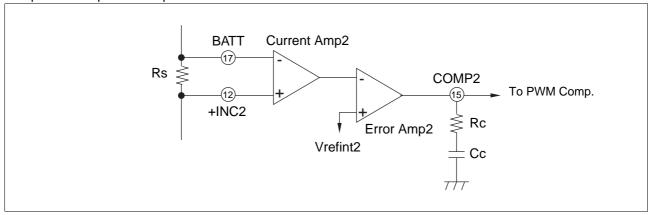

#### (4) Error amplifier block (Error Amp2)

This amplifier detects the output signal from the current detection amplifier (Current Amp2), compares this to the output signal from the charge current control circuit, and outputs a PWM control signal to be used in controlling the charge current.

In addition, a stable phase compensation can be made available to the system by connecting the resistor and the capacitor to the COMP2 pin (pin 15).

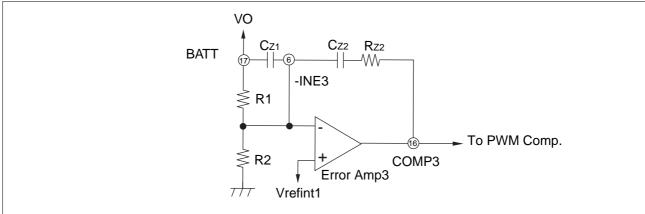

#### (5) Error amplifier block (Error Amp3)

This error amplifier (Error Amp3) detects the output voltage from the DC/DC converter, compares this to the output signal from the VO REFIN controller circuit, and outputs the PWM control signal. Arbitrary output voltage from 2 Cell to 4 Cell can be set by connecting an external resistor of charging voltage to ADJ3 pin (pin 18).

In addition, a stable phase compensation can be made available to the system by connecting the resistor and the capacitor to the COMP3 pin (pin 16).

#### (6) Current detection amplifier block (Current Amp1)

The current detection amplifier (Current Amp1) amplifies the voltage difference between the +INC1 pin (pin 3) and the -INC1 pin (pin 2) by 25 times and outputs the amplified signal to the OUTC1 pin (pin 10).

#### (7) Current detection amplifier block (Current Amp2)

The current detection amplifier (Current Amp2) detects a voltage drop occurring at both ends of the charge current sense resistor (Rs) with the +INC2 pin (pin 12) and the -INC2 pin (pin 13). It outputs the signal amplified by 25 times to the inverted input pin of the following error amplifier (Error Amp2) and to the OUTC2 pin (pin 11).

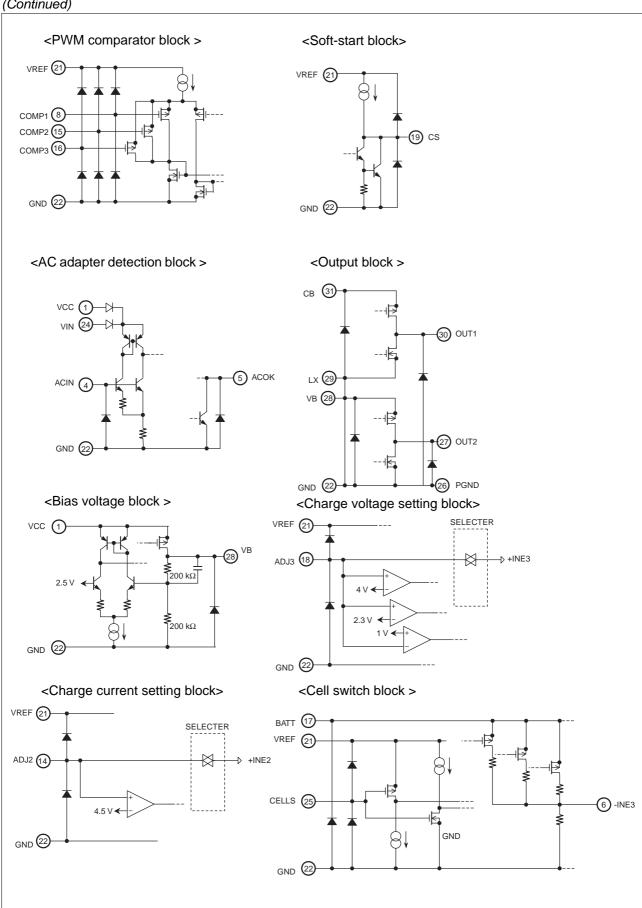

#### (8) PWM comparator block (PWM Comp.)

The PWM comparator circuit is a voltage-pulse width converter for controlling the output duty according to the output voltage of the error amplifiers (Error Amp1 to Error Amp3).

The triangular wave voltage generated by the triangular wave oscillator is compared with the output voltage of one of the three error amplifiers (Error Amp1, Error Amp2 and Error Amp3) that has the lowest potential. The main FET is turned on during the period when the triangular wave voltage is lower than the error amplifier output voltage.

#### (9) Output block (OUT)

The output block uses a CMOS configuration on both the high-side and the low-side, and can drive the external N-ch MOS FET.

#### (10) Power supply control block (CTL1)

The power supply control block controls the DC/DC converter operation. When the CTL1 pin (pin 23) is set to "L" level, the DC/DC converter enters standby mode. In the standby mode, only the AC adapter detection function is operable. (The typical supply current value is  $6 \,\mu\text{A}$  in the standby mode.)

#### CTL1 function table

| CTL1 | DC/DC converter control | AC adapter detection |  |  |  |

|------|-------------------------|----------------------|--|--|--|

| L    | OFF (Standby)           | ON (Active)          |  |  |  |

| Н    | ON (Active)             | ON (Active)          |  |  |  |

#### (11) Current Amp1 control block (CTL2)

The Current Amp1 controller controls the Current Amp1 operation. When the CTL2 pin is set to "H" level, the Current Amp1 becomes operable.

When the CTL1 pin (pin 23) is set to the "L" level and the CTL2 pin (pin32) is set to the "H" level after full-charge, only Current Amp1 and the AC adapter detection function becomes operable.

#### CTL2 function table

| CTL2 | Current Amp1  | AC adapter detection |  |  |  |

|------|---------------|----------------------|--|--|--|

| L    | OFF (Standby) | ON (Active)          |  |  |  |

| Н    | ON (Active)   | ON (Active)          |  |  |  |

#### (12) Bias voltage block (VB)

The bias voltage block outputs 5 V (Typ) for the power supply of the output circuit and for setting the bootstrap voltage.

#### (13) Off time control block (Off Time Control)

When this IC operates by high on-duty, voltage of both ends of bootstrap capacitor CB is decreasing gradually. In such the case, off time control block charges with CB by compulsorily generating off time  $(0.3 \, \mu s \, \text{Typ})$ .

#### 2. Protection Functions

#### (1) Under voltage lockout protection circuit (VREF-UVLO)

A momentary decrease in internal reference voltage (VREF) may cause malfunctions in the control IC, resulting in breakdown or degradation of the system. To prevent such malfunction, the under voltage lockout protection circuit detects internal reference voltage drop and fixes the OUT1 pin (pin 30) and the OUT2 pin (pin 27) at the "L" level. UVLO will be released when the internal reference voltage reaches the threshold voltage of the under voltage lockout protection circuit.

Protection circuit (VREF-UVLO) operation function table

When UVLO is operating (VREF voltage is lower than UVLO threshold voltage.), the logic value of the following pin is fixed.

| OUT1 | OUT2 | CS | VB |

|------|------|----|----|

| L    | L    | L  | L  |

#### (2) Under voltage lockout protection circuit (VCC-UVLO, VB-UVLO)

The transient state or the momentary decrease in power supply voltage, which occurs when the bias voltage (VB) for output circuit is turned on, may cause malfunctions in the control IC, resulting in breakdown or degradation of the system. To prevent such malfunction, the under voltage lockout protection circuit detects a bias voltage drop and fixes the OUT1 pin (pin 30) and the OUT2 pin (pin 27) at the "L" level. UVLO will be released when the power supply voltage or internal reference voltage reaches the threshold voltage of the under voltage lockout protection circuit.

Protection circuit (VCC-UVLO, VB-UVLO) operation function table

When UVLO is operating (VCC voltage or VB voltage is lower than UVLO threshold voltage.), the logical value of the following pin is fixed.

|      | - 31 - |    |

|------|--------|----|

| OUT1 | OUT2   | CS |

| L    | L      | L  |

#### (3) Under input voltage detection block (UV Comp.)

It compares the VCC pin (pin 1) voltage with the BATT pin (pin 17) voltage. If the VCC voltage is lower than the BATT pin voltage plus 0.1 V (Typ), the comparator fixes the OUT1 pin (pin 30) and the OUT2 pin (pin 27) at "L" level.

The system resumes operation when the input voltage is higher than the threshold voltage of the under input voltage detection comparator.

Protection circuit (UV Comp.) operation function table

When under input voltage is detected (Input voltage is lower than UV Comp. threshold voltage), the logical value of the following pin is fixed.

| OUT1 | OUT2 | CS |

|------|------|----|

| L    | L    | L  |

#### (4) Overcurrent detection block (Over Current Det.)

When this block detects that the potential difference between the +INC2 pin (pin 12) and the -INC2 pin (pin 13) exceeds 0.2 V (Typ), and excessive current flows in the charging direction due to a sudden change of load, this block will determine that overcurrent occurs, and sets the CS pin (pin 19) to "L" level and the ON duty to 0%. Afterward, when the overcurrent ceases to exist, the soft-start operation is started.

Overcurrent detection value :  $loc det(A) = \frac{0.2(V)}{Rs(\Omega)}$

#### Charge current and overcurrent detection value by Rs value (example)

| Rs    | ADJ2           | lo               | OCDet |

|-------|----------------|------------------|-------|

| 20 mΩ | 0.5 V to 4.4 V | 0.85 A to 8.65 A | 10 A  |

| 15 mΩ | 0.5 V to 4.4 V | 1.13 A to 11.5 A | 13 A  |

#### (5) Overtemperature detection

The circuit protects an IC from heat destruction. If the temperature at the joint reaches +150 °C, the circuit set OUT1 (pin 30) and OUT2 (pin 27) pins to "L", and stops voltage output.

In addition, if the temperature at the joint drops to +125  $^{\circ}$ C, the voltage output restarts again.

When designing a DC/DC power supply system, do not exceed the absolute maximum ratings of this IC in order to prevent overtemperature protection from being activated.

#### 3. Detection Function

#### AC adapter voltage detection block (AC Comp.)

When the AC adapter voltage detection block (AC Comp.) detects that ACIN pin (pin 4) voltage is below 1.25 V (Typ), it and sets ACOK pin (pin 5) in the AC adapter voltage detection block to Hi-Z. In addition, power is supplied from the VCC pin (pin 1) or the VIN pin (pin 24), whichever has higher voltage. This function operates regardless of the input level of the CTL1 pin (pin 23) and CTL2 pin (pin 32).

AC adapter detection voltage setting

$V_{IN} = Low to High$

$Vth = (R1 + R2) / R2 \times 1.25 V$

$V_{IN}$  = High to Low

$Vth = (R1 + R2) / R2 \times 1.24 V$

#### **■ SETTING THE CHARGE VOLTAGE**

The charge voltage (DC/DC converter output voltage) can be set by the input voltage to ADJ3 pin (pin 18) and CELLS pin (pin 25). The ADJ3 pin can set charge voltage per cell. The value of charge voltage can be freely set when the ADJ3 pin is connected to an external resistor. When the VREF level voltage or the GND level voltage is input to the ADJ3 pin, the internal high-precision reference voltage set in advance can be used. When the VREF level voltage or the GND level voltage is input to the CELLS pin, or the CELLS pin is left unconnected, the number of series batteries can be set.

The correspondence between the ADJ3 pin, the CELLS pin and charge voltage (DC/DC converter output voltage) is shown below.

| ADJ3 pin Input Voltage                                          | CELLS<br>pin | Charge Voltage       | Remarks                                |

|-----------------------------------------------------------------|--------------|----------------------|----------------------------------------|

| VD== :                                                          | GND          | 8.4 V                | 2 Cells × 4.20 V/Cell                  |

| VREF pin<br>(ADJ3 ≥ 4.1V)                                       | OPEN         | 12.6 V               | 3 Cells × 4.20 V/Cell                  |

| (1.200 = 1.11)                                                  | VREF         | 16.8 V               | 4 Cells × 4.20 V/Cell                  |

|                                                                 | GND          | 8.7 V                | 2 Cells × 4.35 V/Cell                  |

| 2.4 V ≤ ADJ3 pin ≤ 3.9 V                                        | OPEN         | 13.05 V              | 3 Cells × 4.35 V/Cell                  |

|                                                                 | VREF         | 17.4 V               | 4 Cells × 4.35 V/Cell                  |

|                                                                 | GND          | 8.0 V                | 2 Cells × 4.00 V/Cell                  |

| GND pin $(0 \text{ V} \leq \text{ADJ3 pin} \leq 0.9 \text{ V})$ | OPEN         | 12.0 V               | 3 Cells × 4.00 V/Cell                  |

| (0 V = 71500 pm = 0.0 V)                                        | VREF         | 16.0 V               | 4 Cells × 4.00 V/Cell                  |

|                                                                 | GND          | 4 × ADJ3 pin voltage | 2 Cells × 2 ×<br>ADJ3 pin voltage/Cell |

| External voltage setting (1.1 V $\leq$ ADJ3 pin $\leq$ 2.2 V)   | OPEN         | 6 × ADJ3 pin voltage | 3 Cells × 2 ×<br>ADJ3 pin voltage/Cell |

|                                                                 | VREF         | 8 × ADJ3 pin voltage | 4 Cells × 2 ×<br>ADJ3 pin voltage/Cell |

#### ADJ3 pin internal circuit

#### ■ SETTING THE CHARGE CURRENT

The error amplifier (Error Amp2) compares the output voltage of charge current control block set by the ADJ2 pin (pin 14) with the output signal from the charge current detection amplifier (Current Amp2), and outputs a the PWM control signal. The maximum charge current for battery can be set according to the ADJ2 pin voltage. When a current exceeding the setting current value is going to flow, constant current charge will be executed at that setting current value, and the charge voltage will drop.

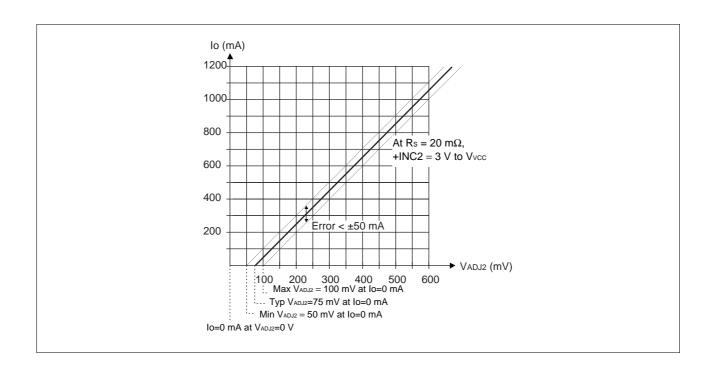

Battery charge current setting voltage: ADJ2

$\label{eq:charge_current_control} Charge \ current \ upper \ limit \ I_o = \frac{Output \ voltage \ in \ the \ charge \ current \ control \ block - 0.075}{Current \ detection \ amplifier \ gain \ (25 \ V/V \ Typ) \ \times \ sense \ resistor \ Rs(\Omega)}$

| AD 10 1 1 1 1                                          | Charge current               | Charge current            |                                  |  |  |

|--------------------------------------------------------|------------------------------|---------------------------|----------------------------------|--|--|

| ADJ2 pin input voltage                                 | control block output voltage | $Rs = 20 \text{ m}\Omega$ | $Rs = 15 \text{ m}\Omega$        |  |  |

| VREF pin<br>(ADJ2 pin ≥ 4.6 V)                         | 1.5 V                        | 2.85 A                    | 3.8 A                            |  |  |

| External Voltage Setting (ADJ2 pin = GND pin to 4.4 V) | Vadj2(V)                     | 2 × (ADJ2 pin – 0.075)(A) | 2.66 × (ADJ2 pin – 0.075)<br>(A) |  |  |

#### • ADJ2 pin internal circuit

#### • Example of the charge current setting (at Rs = 20 m $\Omega$ )

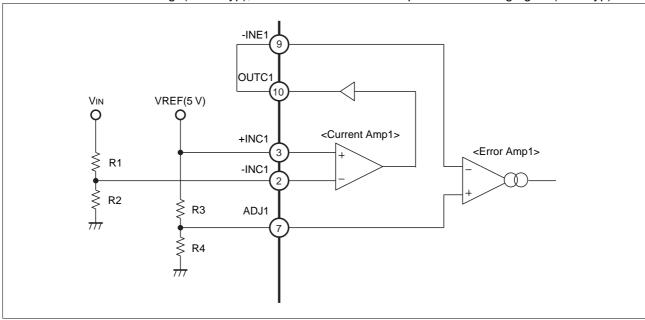

#### ■ SETTING DYNAMICALLY-CONTROLLED CHARGING

With the connection shown below, when the voltage of the AC adapter  $(V_{IN})$  drops and reaches Vth, the result of the equation shown below, the converter becomes dynamically-controlled charging mode and then controls charge current to maintain a constant power level of the AC adapter.

AC adapter voltage in dynamically-controlled-charging mode: Vth

$$Vth = [(1 - \frac{1}{Av} \times \frac{R4}{R3 + R4})VREF + 3 mV] \times \frac{R1 + R2}{R2}$$

VREF = Reference voltage(5.0 V Typ), Av = Current detection amplifier block voltage gain (25.0 Typ)

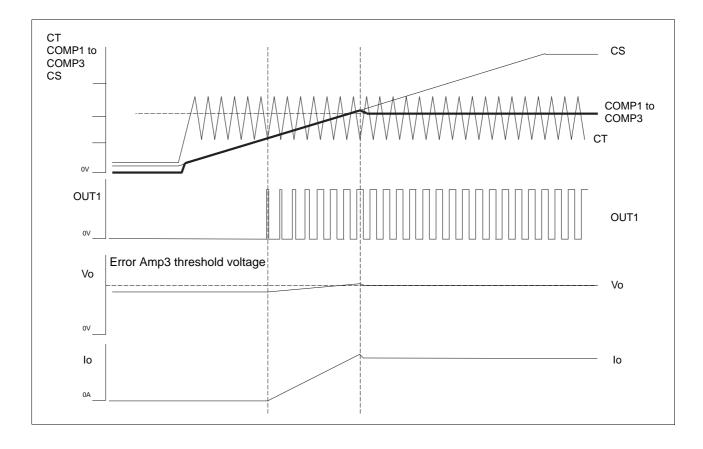

#### ■ SETTING THE SOFT-START TIME

To prevent rush current at start-up of IC, the soft-start time can be set by connecting a soft-start capacitor (Cs) to the CS pin (pin 19). When the CTL1 pin (pin 23) and the CTL2 pin (pin 32) are set to "H" level and the IC is started (Vcc  $3 \ge UVLO$  threshold voltage), the external capacitor (Cs) for soft-start (Cs) connected to the CS pin is charged at 10  $\mu$ A.

The output ON duty depends on the result of comparison done by the PWM comparator among the COMP1 pin (pin 8) voltage, the COMP2 pin (pin15) voltage, the COMP3 pin (pin16) voltage and the triangular wave oscillator output voltage (CT). During soft-start, the COMP1 pin, the COMP2 pin, and the COMP3 pin voltages are clamped so that the voltages of those three pins will not exceed the CS pin voltage. Therefore, the output voltage of the DC/DC converter and current increase can be set by the output ON duty in proportion to rise of the CS pin voltage.

The ON duty is affected by the ramp voltage of the COMP1 pin, the COMP2 pin, and the COMP3 pin until the output voltage of one of the three Error Amp reaches the DC/DC converter loop control voltage. Soft-start time is obtained from the following formula.

Soft-start time (time for the output ON duty to reach 80%):  $ts(s) = 0.23 \times Cs (\mu F)$

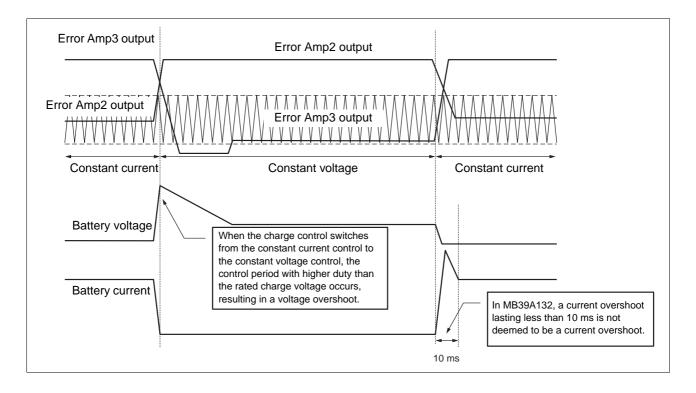

#### **■ TRANSIT RESPONSE AT STEP LOAD CHANGE**

The constant voltage control loop and the constant current control loop are independent of each other . When a load changes suddenly, a control loop is replaced by the other.

Overshoot of the battery voltage and current is generated by the delay occurring in a control loop at a mode change.

The delay time is determined by the phase compensation components values.

When the constant current control changes to the constant voltage control after the battery is removed, the control period with higher duty than the setting charge voltage occurs, resulting in a voltage overshoot. However, since the battery is removed, no excessive voltage is to be applied to the battery.

When the constant voltage control changes to the constant current control after the battery is inserted, the control period with higher duty than the rated charge current occurs, resulting in current overshoot.

In MB39A132, a current overshoot lasting less than 10 ms is not deemed to be a current overshoot.

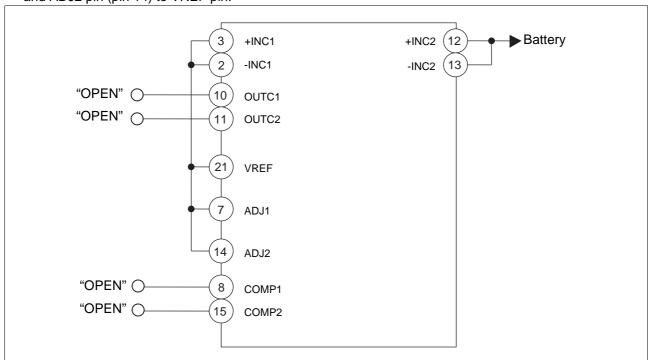

# ■ CONNECTION WITHOUT USING THE CURRENT AMP1, CURRENT AMP2 AND THE ERROR AMP1, ERROR AMP2

When Current Amp1, 2 and Error Amp1, 2 are not used, connect the +INC1 pin (pin 3) and -INC1 pin (pin 2) to VREF pin (pin 21), the +INC2 pin (pin 12) to the -INC2 pin (pin 13), leave the OUTC1 pin (pin 10), OUTC2 pin (pin11), COMP1 pin (pin 8), and COMP2 pin (pin 15) open and connect the ADJ1 pin (pin 7) and ADJ2 pin (pin 14) to VREF pin.

#### ■ I/O EQUIVALENT CIRCUIT

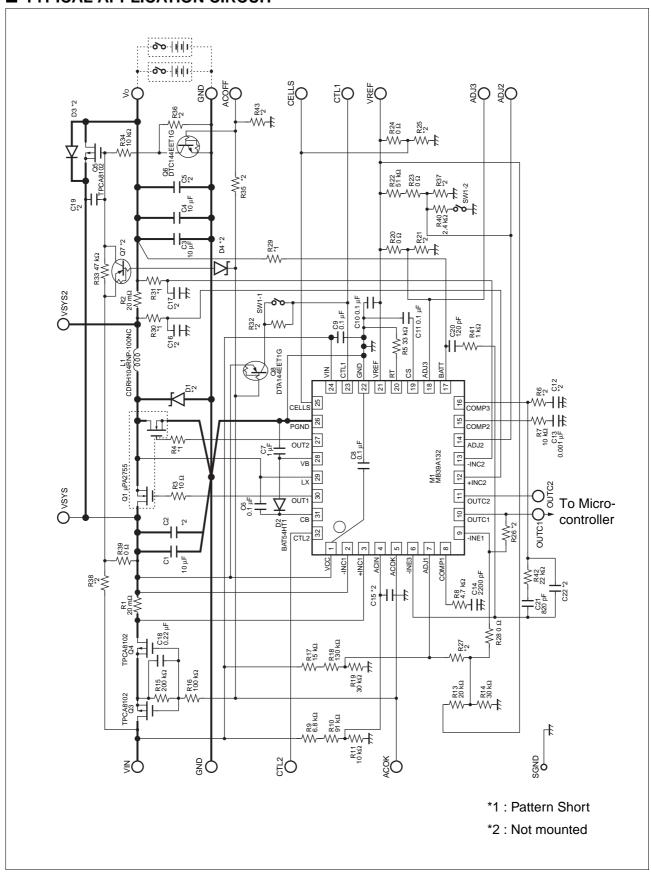

#### **■ TYPICAL APPLICATION CIRCUIT**

#### • Parts list

| Com-<br>ponent | Item              | Specification                     | Vendor  | Package        | Part Number      | Remarks     |

|----------------|-------------------|-----------------------------------|---------|----------------|------------------|-------------|

| M1             | IC                | _                                 | FML     | QFN-32         | MB39A132         |             |

| Q1             | Dual N-ch FET     | VDS = -30  V, $ID = 8  A (Max)$   | NEC     | SOP-8          | μΡΑ2755          |             |

| Q3             | P-ch FET          | VDS = -30  V,<br>ID = 40  A (Max) | TOSHIBA | SOP<br>Advance | TPCA8102         |             |

| Q4             | P-ch FET          | VDS = -30  V,<br>ID = 40  A (Max) | TOSHIBA | SOP<br>Advance | TPCA8102         |             |

| Q5             | P-ch FET          | VDS = -30  V,<br>ID = 40  A (Max) | TOSHIBA | SOP<br>Advance | TPCA8102         |             |

| Q6             | Transistor        | VCEO = 50 V                       | ON Semi | SC-75          | DTC144EET1G      |             |

| Q7             | Transistor        |                                   |         |                |                  | Not mounted |

| Q8             | Transistor        | VCEO = 50 V                       | ON Semi | SC-75          | DTA144EET1G      |             |

| D1             | Diode             |                                   |         |                |                  | Not mounted |

| D2             | Diode             | VF = 0.4 V (Max)<br>at IF = 10 mA | ON Semi | SOD-323        | BAT54HT1         |             |

| D3             | Diode             |                                   |         |                |                  | Not mounted |

| D4             | Diode             |                                   |         |                |                  | Not mounted |

| L1             | Inductor          | 10 μH 35 mΩ<br>Max Irms = 4.4 A   | SUMIDA  | SMD            | CDRH104RNP-100NC |             |

| C1             | Ceramic capacitor | 10 μF(25 V)                       | TDK     | 3216           | C3216JB1E106K    |             |

| C2             | Ceramic capacitor |                                   |         |                |                  | Not mounted |

| C3             | Ceramic capacitor | 10 μF(25 V)                       | TDK     | 3216           | C3216JB1E106K    |             |

| C4             | Ceramic capacitor | 10 μF(25 V)                       | TDK     | 3216           | C3216JB1E106K    |             |

| C5             | Ceramic capacitor |                                   |         |                |                  | Not mounted |

| C6             | Ceramic capacitor | 0.1 μF(50 V)                      | TDK     | 1608           | C1608JB1H104K    |             |

| C7             | Ceramic capacitor | 1 μF(16 V)                        | TDK     | 1608           | C1608JB1C105K    |             |

| C9             | Ceramic capacitor | 0.1 μF(50 V)                      | TDK     | 1608           | C1608JB1H104K    |             |

| C10            | Ceramic capacitor | 0.1 μF(50 V)                      | TDK     | 1608           | C1608JB1H104K    |             |

| C11            | Ceramic capacitor | 0.1 μF(50 V)                      | TDK     | 1608           | C1608JB1H104K    |             |

| C12            | Ceramic capacitor |                                   |         |                |                  | Not mounted |

| C13            | Ceramic capacitor | 0.001 μF(50 V)                    | TDK     | 1608           | C1608JB1H102K    |             |

| C14            | Ceramic capacitor | 2200 pF(50 V)                     | TDK     | 1608           | C1608CH1H222J    |             |

| C15            | Ceramic capacitor |                                   |         |                |                  | Not mounted |

| C16            | Ceramic capacitor |                                   |         |                |                  | Not mounted |

| C17            | Ceramic capacitor |                                   |         |                |                  | Not mounted |

| C18            | Ceramic capacitor | 0.22 μF(25 V)                     | TDK     | 1608           | C1608JB1E224K    |             |

| C19            | Ceramic capacitor |                                   |         |                |                  | Not mounted |

| C20            | Ceramic capacitor | 120 pF(50 V)                      | TDK     | 1608           | C1608CH1H121J    |             |

| C21            | Ceramic capacitor | 820 pF(50 V)                      | TDK     | 1608           | C1608CH1H821J    |             |

| Com-<br>ponent | Item              | Specification | Vendor | Package | Parts No.     | Remarks       |

|----------------|-------------------|---------------|--------|---------|---------------|---------------|

| C22            | Ceramic capacitor |               |        |         |               | Not mounted   |

| R1             | Resistor          | 20 mΩ         | KOA    | SL1     | SL1TTE20L0D   |               |

| R2             | Resistor          | 20 mΩ         | KOA    | SL1     | SL1TTE20L0D   |               |

| R3             | Resistor          | 10 Ω          | SSM    | 1608    | RR0816Q-100-D | Pattern cut   |

| R4             | Resistor          |               |        | 1608    |               | Pattern short |

| R5             | Resistor          | 33 kΩ         | SSM    | 1608    | RR0816P333D   |               |

| R6             | Resistor          |               |        |         |               | Not mounted   |

| R7             | Resistor          | 10 kΩ         | SSM    | 1608    | RR0816P103D   |               |

| R8             | Resistor          | 4.7 kΩ        | SSM    | 1608    | RR0816P472D   |               |

| R9             | Resistor          | 6.8 kΩ        | SSM    | 1608    | RR0816P682D   |               |

| R10            | Resistor          | 91 kΩ         | SSM    | 1608    | RR0816P913D   |               |

| R11            | Resistor          | 10 kΩ         | SSM    | 1608    | RR0816P103D   |               |

| R13            | Resistor          | 20 kΩ         | SSM    | 1608    | RR0816P203D   |               |

| R14            | Resistor          | 30 kΩ         | SSM    | 1608    | RR0816P303D   |               |

| R15            | Resistor          | 200 kΩ        | SSM    | 1608    | RR0816P204D   |               |

| R16            | Resistor          | 100 kΩ        | SSM    | 1608    | RR0816P104D   |               |

| R17            | Resistor          | 15 kΩ         | SSM    | 1608    | RR0816P153D   |               |

| R18            | Resistor          | 130 kΩ        | SSM    | 1608    | RR0816P134D   |               |

| R19            | Resistor          | 30 kΩ         | SSM    | 1608    | RR0816P303D   |               |

| R20            | Resistor          | 0 Ω           | KOA    | 1608    | RK73Z1J       |               |

| R21            | Resistor          |               |        |         |               | Not mounted   |

| R22            | Resistor          | 51 kΩ         | SSM    | 1608    | RR0816P513D   |               |

| R23            | Resistor          | 0 Ω           | KOA    | 1608    | RK73Z1J       |               |

| R24            | Resistor          | 0 Ω           | KOA    | 1608    | RK73Z1J       |               |

| R25            | Resistor          |               |        |         |               | Not mounted   |

| R26            | Resistor          |               |        |         |               | Not mounted   |

| R27            | Resistor          |               |        |         |               | Not mounted   |

| R28            | Resistor          | 0 Ω           | KOA    | 1608    | RK73Z1J       |               |

| R29            | Resistor          |               |        | 1608    |               | Pattern short |

| R30            | Resistor          |               |        | 1608    |               | Pattern short |

| R31            | Resistor          |               |        | 1608    |               | Pattern short |

| R32            | Resistor          |               |        |         |               | Not mounted   |

| R33            | Resistor          | 47 kΩ         | SSM    | 1608    | RR0816P473D   |               |

| R34            | Resistor          | 10 kΩ         | SSM    | 1608    | RR0816P103D   |               |

| R35            | Resistor          |               |        |         |               | Not mounted   |

| R36            | Resistor          |               |        |         |               | Not mounted   |

| R37            | Resistor          |               |        |         |               | Not mounted   |

#### (Continued)

| Com-<br>ponent | Item     | Specification | Vendor | Package | Parts No.   | Remarks     |

|----------------|----------|---------------|--------|---------|-------------|-------------|

| R38            | Resistor |               |        |         |             | Not mounted |

| R39            | Resistor | 0 Ω           | KOA    | 1608    | RK73Z1J     |             |

| R40            | Resistor | 2.4 kΩ        | SSM    | 1608    | RR0816P242D |             |

| R41            | Resistor | 1 kΩ          | SSM    | 1608    | RR0816P102D |             |

| R42            | Resistor | 22 kΩ         | SSM    | 1608    | RR0816P223D |             |

| R43            | Resistor |               |        |         |             | Not mounted |

FML : Fujitsu Microelectronics Limited

NEC : NEC Electronics Corporation

TOSHIBA : TOSHIBA Corporation

ON Semi : ON Semiconductor Corporation

SUMIDA : SUMIDA Corporation

TDK : TDK Corporation

KOA : KOA Corporation SSM : SUSUMU Co.,Ltd

#### ■ APPLICATION NOTE

#### Inductor selection

As a rough guide, the inductance of an inductor should keep the peak-to-peak value of inductor ripple current below 50% of the maximum charge current. The inductance fulfilling the above condition can be found by the following formula.

$$L \ge \frac{V_{\text{IN}} - V_{\text{O}}}{LOR \times I_{\text{OMAX}}} \times \frac{V_{\text{O}}}{V_{\text{IN}} \times fosc}$$

L : Inductance [H]

IOMAX: Maximum charge current [A]

LOR: Inductor ripple current peak to peak value - Maximum charge current ratio (0.5)

V<sub>IN</sub>: Switching power-supply voltage [V]

Vo : Charge voltage [V]

fosc : Switching frequency [Hz]

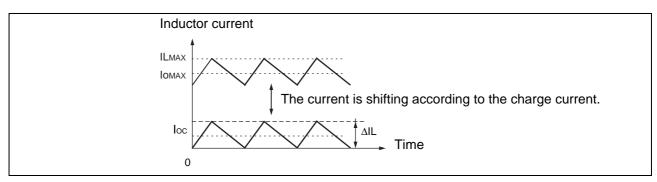

The minimum charge current (critical current) in the condition that inductor current does not flow in reverse can be found by the following formula.

$$loc = \frac{V_0}{2 \times L} \times \frac{V_{IN} - V_0}{V_{IN} \times fosc}$$

loc : Critical current [A]

L : Inductance [H]

V<sub>IN</sub>: Switching power-supply voltage [V]

Vo : Charge voltage [V]

fosc : Switching frequency [Hz]

The maximum value of the current flowing through the inductor needs to be found in order to determine whether the current flowing through the inductor is within the rated value. The maximum current flowing through the inductor can be found by the following formula.

$$IL_{MAX} \ge IO_{MAX} + \frac{\Delta IL}{2}$$

ILMAX: Maximum inductor current [A]

IOMAX: Maximum charge current [A]

$\Delta IL$ : Inductor ripple current peak to peak value [A]

$$\Delta IL \ge \frac{V_{IN} - V_{O}}{L} \times \frac{V_{O}}{V_{IN} \times fosc}$$

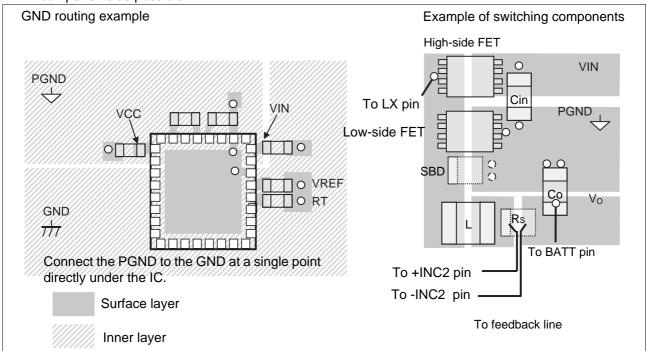

#### SWFET selection