## SEMICONDUCTOR TECHNICAL DATA

## Product Preview

# **Quad High-Side and Octal Low-Side Switch for Automotive**

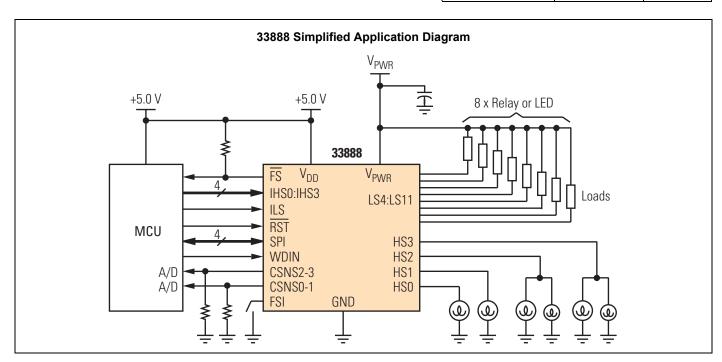

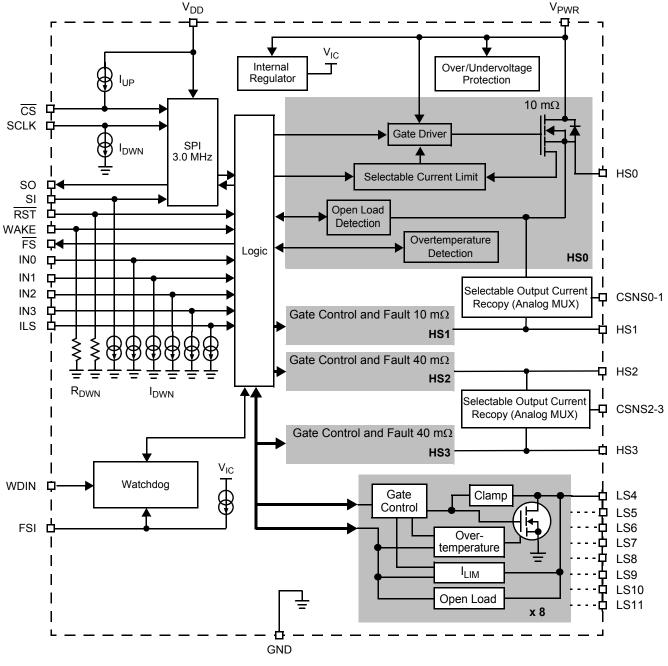

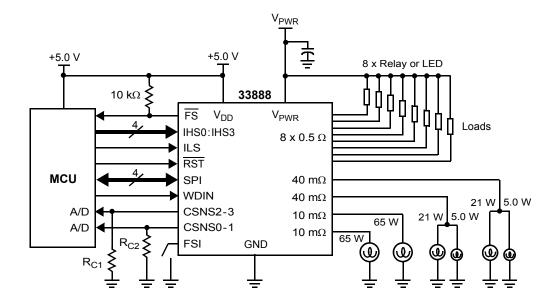

The 33888 is a single-package combination of a power die with four discrete high-side MOSFETs (two 10 m $\Omega$  and two 40 m $\Omega$ ) and an integrated IC control die consisting of eight low-side drivers (600 m $\Omega$  each) with appropriate control, protection, and diagnostic features.

Programming, control, and diagnostics are accomplished using a 16-bit SPI interface. Additionally, each high-side output has its own parallel input for pulse-width modulation (PWM) control if desired. The low sides share a single configurable direct input.

The 33888 is available in two power packages.

#### **Features**

- Dual 10 m $\Omega$  High Side, Dual 40 m $\Omega$  High Side, Octal 600 m $\Omega$  Low Side

- Full Operating Voltage of 6.0 V to 27 V

- SPI Control of High-Side Overcurrent Limit, High Side Current Sense, Output OFF Open Load Detection, Output ON/OFF Control, Watchdog Timeout

- · SPI Reporting of Program Status and Fault

- · High-Side Analog Current Feedback with Selectable Ratio

- Enhanced 16 V Reverse Polarity V<sub>PWR</sub> Protection

# 33888 33888A

## SOLID STATE RELAY FOR **AUTOMOTIVE APPLICATIONS**

**Bottom View**

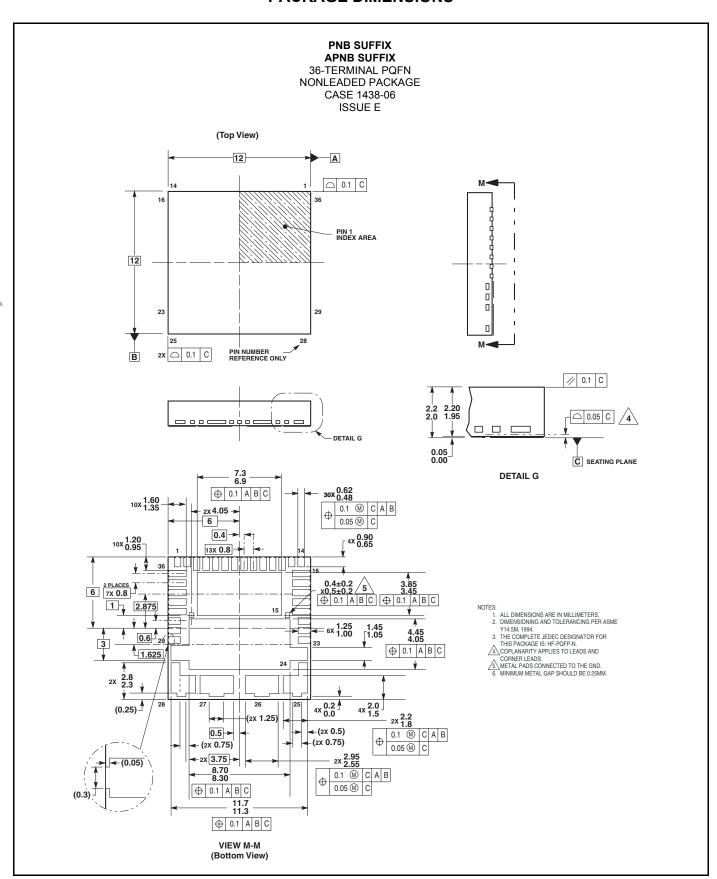

**PNB SUFFIX APNB SUFFIX** CASE 1438-06 **36-TERMINAL PQFN** (12 x 12)

**Top View**

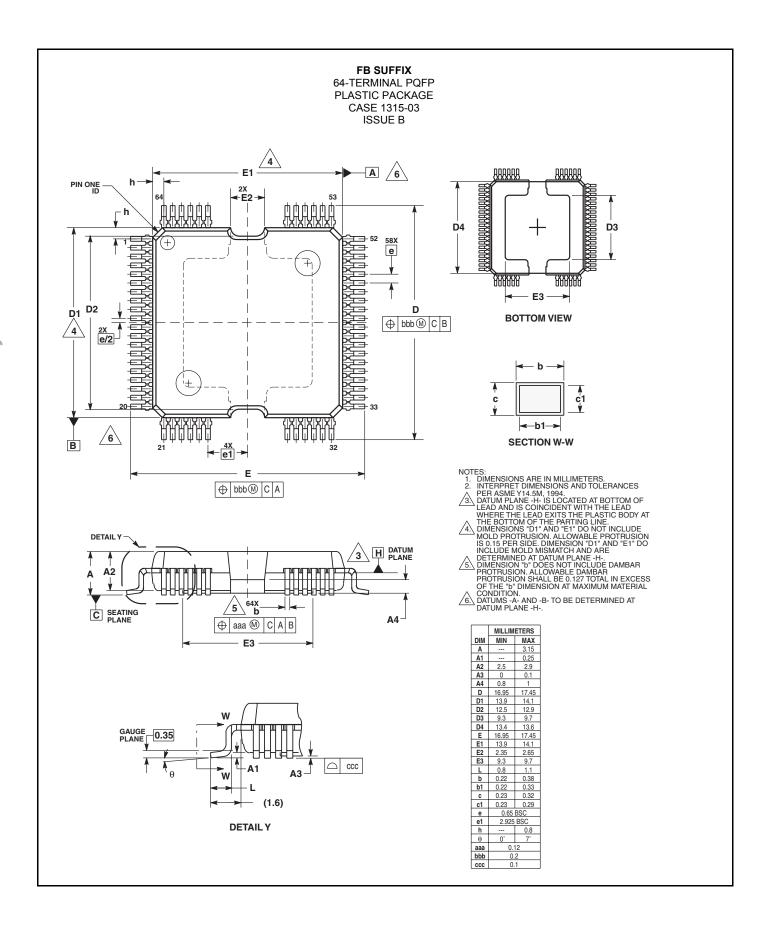

**FB SUFFIX** CASE 1315-03 **64-TERMINAL PQFP**

### **ORDERING INFORMATION**

| Device         | Temperature<br>Range (T <sub>A</sub> ) | Package    |

|----------------|----------------------------------------|------------|

| PC33888PNB/R2  |                                        | 36 PQFN    |

| PC33888APNB/R2 | -40°C to 125°C                         | JO F QI IN |

| MC33888FB/R2   |                                        | 64 PQFP    |

This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

Table 1. Features Comparison: 33888 and 33888A

| Parameter                              | Symbol              | Condition                                            | 33888         | 33888A           | For details,<br>see page |

|----------------------------------------|---------------------|------------------------------------------------------|---------------|------------------|--------------------------|

| Undervoltage Low-Side Output Shutdown  | V <sub>PWRUV</sub>  | _                                                    | 5.0 V         | 3.0 V            | <u>11</u>                |

| Low-Side Drain-to-Source ON Resistance | R <sub>DS(ON)</sub> | V <sub>PWR</sub> = 4.5 V;<br>V <sub>DD</sub> = 3.5 V | Not specified | 8.0 Ω            | <u>14</u>                |

| Recommended Frequency of SPI Operation | f <sub>SPI</sub>    | Extended Mode,<br>V <sub>DD</sub> = 3.4 V            | Not specified | 2.1 MHz<br>(max) | <u>17</u>                |

Figure 1. 33888 Simplified Internal Block Diagram

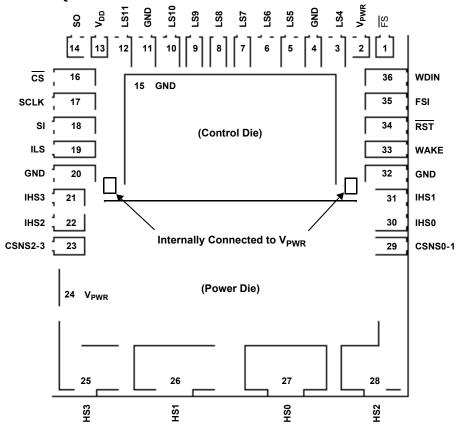

## **Transparent Top View of Package**

## **TERMINAL DEFINITIONS FOR PQFN**

| Terminal             | Terminal<br>Name          | Formal Name                                                                       | Definition                                                                                                                                                                                                                                                                                                 |

|----------------------|---------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | FS                        | Fault Status<br>(Active Low)                                                      | This output terminal is an open drain indication that goes active low when a fault mode is detected by the device. Specific device fault indication is given via the SO terminal.                                                                                                                          |

| 2, 24                | V <sub>PWR</sub>          | Positive Power Supply                                                             | These terminal connects to the positive power supply and are the source input of operational power for the device.                                                                                                                                                                                         |

| 3<br>6<br>8<br>10    | LS4<br>LS6<br>LS8<br>LS10 | Low-Side Output 4<br>Low-Side Output 6<br>Low-Side Output 8<br>Low-Side Output 10 | Each low-side terminal is one 0.6 $\Omega$ low-side output MOSFET drain, which pulls current through the connected loads. Each of the outputs is actively clamped at 53 V. These outputs are current and thermal overload protected. Maximum steady state current through each of these outputs is 500 mA. |

| 4, 11, 15,<br>20, 32 | GND                       | Ground                                                                            | These terminals serve as the ground for the source of the low-side output transistors as well as the logic portion of the device.                                                                                                                                                                          |

| 5<br>7<br>9<br>12    | LS5<br>LS7<br>LS9<br>LS11 | Low-Side Output 5<br>Low-Side Output 7<br>Low-Side Output 9<br>Low-Side Output 11 | Each low-side terminal is one 0.6 $\Omega$ low-side output MOSFET drain, which pulls current through the connected loads. Each of the outputs is actively clamped at 53 V. These outputs are current and thermal overload protected. Maximum steady state current through each of these outputs is 800 mA. |

| 13                   | $V_{DD}$                  | Digital Drain Voltage (Power)                                                     | This is an external input terminal used to supply power to the SPI circuit.                                                                                                                                                                                                                                |

## **TERMINAL DEFINITIONS FOR PQFN (continued)**

| Terminal             | Terminal<br>Name             | Formal Name                                                                      | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

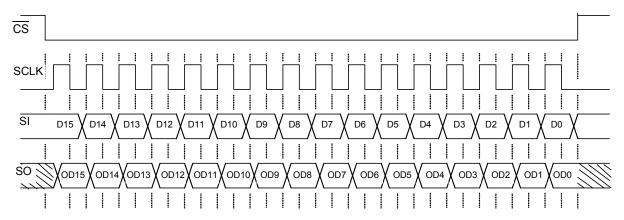

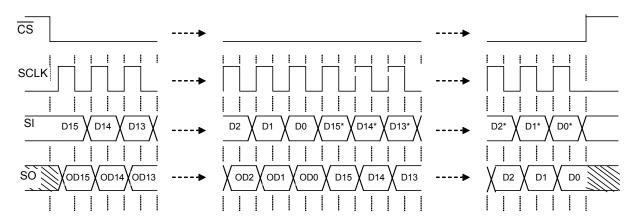

| 14                   | SO                           | Serial Output                                                                    | This is an output terminal connected to the SPI Serial Data Input terminal of the MCU or to the SI terminal of the next device in a daisy chain. This output will remain tri-stated unless the device is selected by a low $\overline{\text{CS}}$ terminal. The output signal generated will have CMOS logic levels and the output data will transition on the rising edges of SCLK. The serial output data provides fault information for each output and is returned MSB first when the device is addressed. OD11 through OD0 are output fault bits for outputs 11 through 0, respectively. |

| 16                   | CS                           | Chip Select<br>(Active Low)                                                      | This is an input terminal connected to a chip select output of a microcontroller (MCU). This IC controls which device is addressed (selected) by pulling the $\overline{\text{CS}}$ terminal of the desired device logic Low, enabling the SPI communication with the device, while other devices on the serial link keep their serial outputs tri-stated. This input has an internal active pullup and requires CMOS logic levels.                                                                                                                                                           |

| 17                   | SCLK                         | Serial Clock                                                                     | This input terminal is connected to the SCLK terminal of the master MCU, which is a bit (shift) clock for the SPI port. It transitions one time per bit transferred at an operating frequency, f <sub>SPI</sub> , and is idle between command transfers. It is 50% duty cycle and has CMOS logic levels. This signal is used to shift data to and from the 33888.                                                                                                                                                                                                                             |

| 18                   | SI                           | Serial Input                                                                     | This input terminal is connected to the SPI Serial Data Output terminal of the MCU from which it receives output command data. This input has an internal active pull-down and requires CMOS logic levels. The serial data transmitted on this line is a 16-bit control command sent MSB first, which controls the twelve output channels. Bits D3:D0 control the high-side outputs HS3:HS0, respectively. Bits D11:D4 control the low-side outputs LS11:LS4, respectively. The MUC will ensure that data is available on the falling edge of SCLK.                                           |

| 19                   | ILS                          | Low-Side Input                                                                   | This input terminal is used to directly control a number of the low-side devices as configured by SPI. This terminal may or may not be activated depending on the configured state of the internal logic.                                                                                                                                                                                                                                                                                                                                                                                     |

| 21<br>22<br>30<br>31 | IHS3<br>IHS2<br>IHS0<br>IHS1 | High-Side Input 3<br>High-Side Input 2<br>High-Side Input 0<br>High-Side Input 1 | Each high-side input terminal is used to directly control only one designated high-<br>side output. These inputs may or may not be activated depending on the configured<br>state of the internal logic.                                                                                                                                                                                                                                                                                                                                                                                      |

| 23<br>29             | CSNS2-3<br>CSNS0-1           | Current Sense 2-3<br>Current Sense 0-1                                           | These terminals deliver a ratioed amount of the high-side output current that can be used to generate signal ground referenced output voltages for use by the MCU. Each respective CSNS terminal can be configured via SPI to deliver current from either of the two assigned outputs, or the currents could be the sum of the two. Current from HS0 and/or HS1 are sensed via CSNS0-1. Current from HS2 and/or HS3 are sensed via CSNS2-3.                                                                                                                                                   |

| 25<br>28             | HS3<br>HS2                   | High-Side Output 3<br>High-Side Output 2                                         | Each terminal is the source of a 40 m $\Omega$ MOSFET high-side driver, which delivers current through the connected loads. These outputs can be controlled via SPI or using the IHS terminals depending on the internal configuration. These outputs are current limited and thermally protected. During fail-safe mode, output HS2 will be turned on until the device is reinitialized and then immediately followed by normal operation.                                                                                                                                                   |

| 26<br>27             | HS1<br>HS0                   | High-Side Output 1<br>High-Side Output 0                                         | Each terminal is the source of a 10 m $\Omega$ MOSFET high-side driver, which delivers current through the connected loads. These outputs can be controlled via SPI or using the IHS terminals depending on the internal configuration. These outputs are current limited and thermally protected. During fail-safe mode, output HS0 will be turned on until the device is reinitialized and then immediately followed by normal operation.                                                                                                                                                   |

| 33                   | WAKE                         | Wake                                                                             | This terminal is used to input a logic [1] signal in order to enable the watchdog timer function. An internal clamp protects the terminal from high voltages when current is limited with an external resistor. This input has a passive internal pulldown.                                                                                                                                                                                                                                                                                                                                   |

## **TERMINAL DEFINITIONS FOR PQFN (continued)**

| Terminal | Terminal<br>Name | Formal Name        | Definition                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34       | RST              | Reset (Active Low) | This input terminal is used to initialize the device configuration and fault registers, as well as place the device in a low current standby mode. This terminal also starts the watchdog timeout when transitioned from logic [0] to logic [1]. This terminal should not be allowed to be at logic [1] until V <sub>DD</sub> is in regulation. This input has an internal passive pulldown.                        |

| 35       | FSI              | Fail-Safe Input    | The Fail-Safe input terminal level determines the state of the outputs after a watchdog timeout occurs. This terminal has an internal pullup. If the FSI terminal is left to float to a logic [1], then HS0 and HS2 will turn on when in the Fail-Safe state. If the FSI terminal is tied to GND, the watchdog circuit and fail-safe operation will be disabled, thus allowing operation without a watchdog signal. |

| 36       | WDIN             | Watchdog Input     | This input terminal is a CMOS logic level input that is used to monitor system operation. If the incoming watchdog signal does not transition within the normal watchdog timeout range, the device will operate in the Fail-Safe mode. This input has an active internal pulldown.                                                                                                                                  |

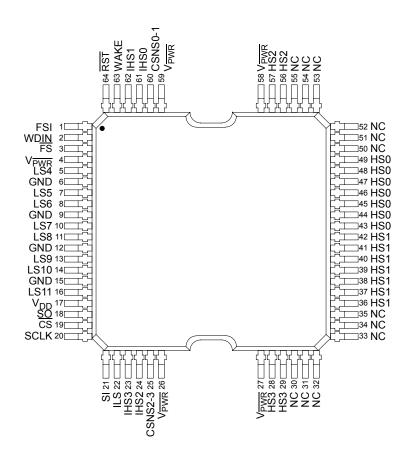

### **TERMINAL DEFINITIONS FOR PQFP**

Functional descriptions of many of these terminals can be found in the System/Application Information section beginning on page 19.

| Terminal             | Terminal<br>Name          | Formal Name                                                                       | Definition                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|---------------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | FSI                       | Fail-Safe Input                                                                   | The Fail-Safe input terminal level determines the state of the outputs after a watchdog timeout occurs. This terminal has an internal pullup. If the FSI terminal is left to float to a logic [1], then HS0 and HS2 will turn on when in the Fail-Safe state. If the FSI terminal is tied to GND, the watchdog circuit and fail-safe operation will be disabled, thus allowing operation without a watchdog signal. |

| 2                    | WDIN                      | Watchdog Input                                                                    | This input terminal is a CMOS logic level input that is used to monitor system operation. If the incoming watchdog signal does not transition within the normal watchdog timeout range, the device will operate in the Fail-Safe mode. This input has an active internal pulldown.                                                                                                                                  |

| 3                    | FS                        | Fault Status<br>(Active Low)                                                      | This output terminal is an open drain indication that goes active low when a fault mode is detected by the device. Specific device fault indication is given via the SO terminal.                                                                                                                                                                                                                                   |

| 4, 26, 27,<br>58, 59 | V <sub>PWR</sub>          | Positive Power Supply                                                             | These terminal connects to the positive power supply and are the source input of operational power for the device.                                                                                                                                                                                                                                                                                                  |

| 5<br>8<br>11<br>14   | LS4<br>LS6<br>LS8<br>LS10 | Low-Side Output 4<br>Low-Side Output 6<br>Low-Side Output 8<br>Low-Side Output 10 | Each low-side terminal is one 0.6 $\Omega$ low-side output MOSFET drain, which pulls current through the connected loads. Each of the outputs is actively clamped at 53 V. These outputs are current and thermal overload protected. Maximum steady state current through each of these outputs is 500 mA.                                                                                                          |

| 6, 9, 12, 15         | GND                       | Ground                                                                            | These terminals serve as the ground for the source of the low-side output transistors as well as the logic portion of the device.                                                                                                                                                                                                                                                                                   |

Go to: www.freescale.com

## **TERMINAL DEFINITIONS FOR PQFP (continued)**

| Terminal             | Terminal<br>Name             | Formal Name                                                                       | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------|------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>10<br>13<br>16  | LS5<br>LS7<br>LS9<br>LS11    | Low-Side Output 5<br>Low-Side Output 7<br>Low-Side Output 9<br>Low-Side Output 11 | Each low-side terminal is one 0.6 $\Omega$ low-side output MOSFET drain, which pulls current through the connected loads. Each of the outputs is actively clamped at 53 V. These outputs are current and thermal overload protected. Maximum steady state current through each of these outputs is 800 mA.                                                                                                                                                                                                                                                                                    |

| 17                   | $V_{DD}$                     | Digital Drain Voltage (Power)                                                     | This is an external input terminal used to supply power to the SPI circuit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18                   | SO                           | Serial Output                                                                     | This is an output terminal connected to the SPI Serial Data Input terminal of the MCU or to the SI terminal of the next device in a daisy chain. This output will remain tri-stated unless the device is selected by a low $\overline{\text{CS}}$ terminal. The output signal generated will have CMOS logic levels and the output data will transition on the rising edges of SCLK. The serial output data provides fault information for each output and is returned MSB first when the device is addressed. OD11 through OD0 are output fault bits for outputs 11 through 0, respectively. |

| 19                   | CS                           | Chip Select<br>(Active Low)                                                       | This is an input terminal connected to a chip select output of a microcontroller (MCU). This IC controls which device is addressed (selected) by pulling the $\overline{\text{CS}}$ terminal of the desired device logic Low, enabling the SPI communication with the device, while other devices on the serial link keep their serial outputs tri-stated. This input has an internal active pullup and requires CMOS logic levels.                                                                                                                                                           |

| 20                   | SCLK                         | Serial Clock                                                                      | This input terminal is connected to the SCLK terminal of the master MCU, which is a bit (shift) clock for the SPI port. It transitions one time per bit transferred at an operating frequency, f <sub>SPI</sub> , and is idle between command transfers. It is 50% duty cycle and has CMOS logic levels. This signal is used to shift data to and from the 33888.                                                                                                                                                                                                                             |

| 21                   | SI                           | Serial Input                                                                      | This input terminal is connected to the SPI Serial Data Output terminal of the MCU from which it receives output command data. This input has an internal active pull-down and requires CMOS logic levels. The serial data transmitted on this line is a 16-bit control command sent MSB first, which controls the twelve output channels. Bits D3:D0 control the high-side outputs HS3:HS0, respectively. Bits D11:D4 control the low-side outputs LS11:LS4, respectively. The MUC will ensure that data is available on the falling edge of SCLK.                                           |

| 22                   | ILS                          | Low-Side Input                                                                    | This input terminal is used to directly control a number of the low-side devices as configured by SPI. This terminal may or may not be activated depending on the configured state of the internal logic.                                                                                                                                                                                                                                                                                                                                                                                     |

| 23<br>24<br>61<br>62 | IHS3<br>IHS2<br>IHS0<br>IHS1 | High-Side Input 3<br>High-Side Input 2<br>High-Side Input 0<br>High-Side Input 1  | Each high-side input terminal is used to directly control only one designated high-side output. These inputs may or may not be activated depending on the configured state of the internal logic.                                                                                                                                                                                                                                                                                                                                                                                             |

| 25<br>60             | CSNS2-3<br>CSNS0-1           | Current Sense 2-3<br>Current Sense 0-1                                            | These terminals deliver a ratioed amount of the high-side output current that can be used to generate signal ground referenced output voltages for use by the MCU. Each respective CSNS terminal can be configured via SPI to deliver current from either of the two assigned outputs, or the currents could be the sum of the two. Current from HS0 and/or HS1 are sensed via CSNS0-1. Current from HS2 and/or HS3 are sensed via CSNS2-3.                                                                                                                                                   |

| 28, 29<br>56, 57     | HS3<br>HS2                   | High-Side Output 3<br>High-Side Output 2                                          | Each terminal is the source of a 40 m $\Omega$ MOSFET high-side driver, which delivers current through the connected loads. These outputs can be controlled via SPI or using the IHS terminals depending on the internal configuration. These outputs are current limited and thermally protected. During fail-safe mode, output HS2 will be turned on until the device is reinitialized and then immediately followed by normal operation.                                                                                                                                                   |

| 30-35,<br>50-55      | NC                           | Not Connected                                                                     | These terminals are not connected internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

## **TERMINAL DEFINITIONS FOR PQFP (continued)**

| Terminal       | Terminal<br>Name | Formal Name                              | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36–42<br>43–49 | HS1<br>HS0       | High-Side Output 1<br>High-Side Output 0 | Each terminal is the source of a 10 m $\Omega$ MOSFET high-side driver, which delivers current through the connected loads. These outputs can be controlled via SPI or using the IHS terminals depending on the internal configuration. These outputs are current limited and thermally protected. During fail-safe mode, output HS0 will be turned on until the device is reinitialized and then immediately followed by normal operation. |

| 63             | WAKE             | Wake                                     | This terminal is used to input a logic [1] signal in order to enable the watchdog timer function. An internal clamp protects the terminal from high voltages when current is limited with an external resistor. This input has a passive internal pulldown.                                                                                                                                                                                 |

| 64             | RST              | Reset (Active Low)                       | This input terminal is used to initialize the device configuration and fault registers, as well as place the device in a low current standby mode. This terminal also starts the watchdog timeout when transitioned from logic [0] to logic [1]. This terminal should not be allowed to be at logic [1] until $V_{DD}$ is in regulation. This input has an internal passive pulldown.                                                       |

### **MAXIMUM RATINGS**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                                                   | Symbol                                                | Value            | Unit |

|------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|------|

| ELECTRICAL RATINGS                                                                       | ·                                                     |                  |      |

| Power Supply Voltage<br>Steady State                                                     | V <sub>PWR</sub>                                      | -16 to 41        | V    |

| Input Terminal Voltage (Note 1)                                                          | V <sub>IN</sub>                                       | -0.3 to 7.0      | V    |

| WAKE Input Terminal Clamp Current                                                        | I <sub>WICI</sub>                                     | 2.5              | mA   |

| Continuous per Output Current (Note 2) Low-Sides 4, 6, 8, 10 Low-Sides 5, 7, 9, 11       | loutls                                                | 500<br>800       | mA   |

| Continuous per Output Current (Note 3) High-Sides 0, 1 High-Sides 2, 3                   | Гоитнѕ                                                | 10<br>5.0        | A    |

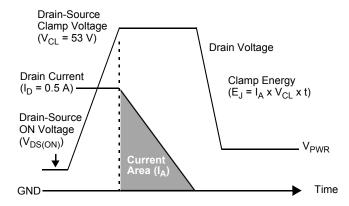

| Output Clamp Energy High-Sides 0, 1 (Note 4) High-Sides 2, 3 (Note 5) Low-Sides (Note 6) | E <sub>HS</sub><br>E <sub>HS</sub><br>E <sub>LS</sub> | 450<br>120<br>50 | mJ   |

| ESD Voltage Human Body Model (Note 7) Machine Model (Note 8)                             | V <sub>ESD1</sub>                                     | ±2000<br>±200    | V    |

- 1. Exceeding voltage limits on SCLK, SI,  $\overline{\text{CS}}$ , WDIN,  $\overline{\text{RST}}$ , IHS, FSI, or ILS terminals may cause a malfunction or permanent damage to the device

- 2. Continuous low-side output current rating so long as maximum junction temperature is not exceeded. Operation at 125°C ambient temperature will require calculation of maximum output current using package thermal resistance.

- 3. Continuous high-side output current rating so long as maximum junction temperature is not exceeded. Operation at 125°C ambient temperature will require calculation of maximum output current using package thermal resistance.

- 4. Active HS0 and HS1 clamp energy using the following conditions: single nonrepetitive pulse, V<sub>PWR</sub> = 16.0 V, L = 40 mH, T<sub>J</sub> = 150°C.

- 5. Active HS2 and HS3 clamp energy using the following conditions: single nonrepetitive pulse, V<sub>PWR</sub> = 16.0 V, L = 10 mH, T<sub>J</sub> = 150°C.

- 6. Active low-side clamp energy using the following conditions: single nonrepetitive pulse, 450 mA,  $T_J$  = 150°C.

- 7. ESD1 testing is performed in accordance with the Human Body Model ( $C_{ZAP} = 100 \text{ pF}, R_{ZAP} = 1500 \Omega$ ).

- 8. ESD2 testing is performed in accordance with the Machine Model ( $C_{ZAP} = 200 \text{ pF}, R_{ZAP} = 0 \Omega$ ).

### **MAXIMUM RATINGS (continued)**

All voltages are with respect to ground unless otherwise noted.

| Rating                                                                  | Symbol              | Value      | Unit |

|-------------------------------------------------------------------------|---------------------|------------|------|

| THERMAL RATINGS                                                         |                     |            |      |

| Operating Temperature                                                   |                     |            | °C   |

| Ambient                                                                 | $T_A$               | -40 to 125 |      |

| Junction                                                                | $T_J$               | -40 to 150 |      |

| Storage Temperature                                                     | T <sub>STG</sub>    | -55 to 150 | °C   |

| Control Die Thermal Resistance (Note 9)                                 | $R_{\theta CJC}$    |            | °C/W |

| PQFP                                                                    |                     |            |      |

| One Low-Side ON                                                         |                     | 12.5       |      |

| Two Low-Side ON                                                         |                     | 9.3        |      |

| Three Low-Side ON                                                       |                     | 7.3        |      |

| Four Low Side ON                                                        |                     | 5.9        |      |

| All Low-Sides ON                                                        |                     | 3.2        |      |

| PQFN                                                                    |                     |            |      |

| One Low-Side ON                                                         |                     | 8.6        |      |

| Two Low-Side ON                                                         |                     | 6.0        |      |

| Three Low-Side ON                                                       |                     | 4.6        |      |

| Four Low Side ON                                                        |                     | 3.8        |      |

| All Low-Sides ON                                                        |                     | 2.0        |      |

| Power Die Thermal Resistance (Note 9)                                   | $R_{	heta PJC}$     |            | °C/W |

| PQFP                                                                    |                     | _          |      |

| One High-Side 2, 3 ON                                                   |                     | 0.5        |      |

| All High-Sides ON                                                       |                     | 0.15       |      |

| PQFN                                                                    |                     |            |      |

| One High-Side 2, 3 ON                                                   |                     | 0.5        |      |

| All High-Sides ON                                                       |                     | 0.1        |      |

| Thermal Resistance, Junction to Ambient, Natural Convection, Four-Layer | $R_{	heta JA}$      |            | °C/W |

| Board (Note 9)                                                          |                     | 33         |      |

| PQFP                                                                    |                     | 37         |      |

| PQFN                                                                    |                     |            |      |

| Peak Terminal Reflow Temperature During Solder Mounting (Note 10)       | T <sub>SOLDER</sub> |            | °C   |

| PQFP                                                                    |                     | 225        |      |

| PQFN                                                                    |                     | 240        |      |

- 9. Board dimensions are 8.0 cm x 8.0 cm x 1.5 mm with a 300 mm<sup>2</sup> copper area on the bottom layer.

- 10. Terminal soldering temperature limit is 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

### STATIC ELECTRICAL CHARACTERISTICS

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                    | Symbol                  | Min  | Тур | Max | Unit |

|-------------------------------------------------------------------------------------------------------------------|-------------------------|------|-----|-----|------|

| POWER INPUT                                                                                                       |                         | •    | •   |     |      |

| Supply Voltage Range                                                                                              | V <sub>PWR</sub>        |      |     |     | V    |

| Fully Operational                                                                                                 |                         | 6.0  | _   | 27  |      |

| V <sub>PWR</sub> Supply Current                                                                                   | I <sub>PWR(ON)</sub>    |      |     |     | mA   |

| T <sub>J</sub> > 125°C                                                                                            |                         | _    | 17  | 25  |      |

| $T_{J} \le 125^{\circ}C$                                                                                          |                         | _    | _   | 20  |      |

| $V_{PWR}$ Standby Current (All Outputs OFF, Open Load Detection Disabled, WAKE = H, $\overline{RST}$ = H)         | I <sub>PWR(SBY)</sub>   |      |     |     | mA   |

| T <sub>J</sub> > 125°C                                                                                            |                         | _    | 4.2 | 7.0 |      |

| $T_{J} \le 125^{\circ}C$                                                                                          |                         | _    | 2.9 | 5.0 |      |

| Sleep State Supply Current ( $V_{PWR}$ < 12.6 V, $\overline{RST}$ < 0.5 V, WAKE < 0.5 V, HS[0:3] = 0 V) (Note 11) | I <sub>PWR(SS)</sub>    |      |     |     | μА   |

| $T_J = 85^{\circ}C$                                                                                               |                         | _    | -   | 80  |      |

| $T_J = 25^{\circ}C$                                                                                               |                         | _    | 1.0 | 25  |      |

| Logic Supply Voltage Range                                                                                        | V <sub>DD</sub>         | 4.5  | 5.0 | 5.5 | V    |

| Logic Supply Current                                                                                              | I <sub>DD(ON)</sub>     |      |     |     | mA   |

| T <sub>J</sub> > 125°C                                                                                            |                         | _    | 4.2 | 7.0 |      |

| $T_{J} \le 125^{\circ}C$                                                                                          |                         | -    | 2.9 | 5.0 |      |

| Logic Supply Sleep State Current                                                                                  | I <sub>DD(SS)</sub>     | _    | -   | 5.0 | μА   |

| Sleep State Low-Side Output Leakage Current (per Low-Side Output, RST = LOW)                                      | I <sub>SLK(SS)</sub>    |      |     |     | μА   |

| $T_J = 85^{\circ}C$                                                                                               |                         | _    | -   | 3.0 |      |

| $T_J = 25^{\circ}C$                                                                                               |                         | _    | _   | 1.0 |      |

| Overvoltage Shutdown Threshold                                                                                    | V <sub>PWROV</sub>      | 28.5 | 32  | 36  | V    |

| Overvoltage Shutdown Hysteresis                                                                                   | V <sub>PWROV(HYS)</sub> | 0.2  | 0.6 | 1.5 | V    |

| Undervoltage High-Side Output Shutdown (Note 12)                                                                  | V <sub>PWRUV</sub>      | 5.0  | 5.6 | 6.0 | V    |

| Undervoltage Low-Side Output Shutdown                                                                             | V <sub>PWRUV</sub>      |      |     |     | V    |

| APNB Suffix Only (Note 12)                                                                                        |                         | 3.0  | 4.0 | 4.4 |      |

| PNB and FB Suffixes                                                                                               |                         | 5.0  | 5.6 | 6.0 |      |

| Undervoltage High-Side Shutdown Hysteresis                                                                        | V <sub>PWRUV(HYS)</sub> | 0.1  | 0.3 | 0.5 | V    |

- 11. This parameter is tested at 125  $^{\circ}$ C with a maximum value of 10  $\mu$ A.

- 12. SPI/IO and internal logic operational. Outputs will recover in instructed state when V<sub>PWR</sub> voltage level returns to normal as long as the level does not go below V<sub>PWRUV</sub>.

### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions  $6.0 \text{ V} \le \text{V}_{PWR} \le 27 \text{ V}, 4.5 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, -40 ^{\circ}\text{C} \le \text{T}_{J} \le 150 ^{\circ}\text{C}$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $\text{T}_{A}$  = 25  $^{\circ}\text{C}$  under nominal conditions unless otherwise noted.

| Characteristic                                                                                   | Symbol                   | Min   | Тур    | Max   | Unit |

|--------------------------------------------------------------------------------------------------|--------------------------|-------|--------|-------|------|

| POWER INPUT (continued)                                                                          |                          |       |        |       |      |

| Current Sense Ratio (9.0 V ≤ V <sub>PWR</sub> ≤ 16 V, CSNS ≤ 4.5 V)                              | C <sub>SR[0:1]</sub>     |       |        |       | _    |

| CSNS0-1/HS0, CSNS0-1/HS1                                                                         |                          | -     | 1/1400 | _     |      |

| Current Sense Ratio (C <sub>SR[0:1]</sub> ) Accuracy                                             | C <sub>SR[0:1]_ACC</sub> |       |        |       | %    |

| HS[0:1] Output Current                                                                           |                          |       |        |       |      |

| 1.0 A                                                                                            |                          | -35   | _      | 35    |      |

| 2.0 A                                                                                            |                          | -19   | -      | 19    |      |

| 5.0 A                                                                                            |                          | -14   | -      | 14    |      |

| 6.5 A                                                                                            |                          | -12   | _      | 12    |      |

| 10 A                                                                                             |                          | -12   | _      | 12    |      |

| Current Sense Ratio (V <sub>PWR</sub> = 9.0 V – 16 V, CSNS < 4.5 V)                              | C <sub>SR</sub>          |       |        |       | _    |

| CSNS2-3/HS2, CSNS2-3/HS3                                                                         |                          | _     | 1/880  | _     |      |

| Current Sense Ratio (C <sub>SR[2:3]</sub> ) Accuracy                                             | C <sub>SR[2:3]_ACC</sub> |       |        |       | %    |

| HS[2:3] Output Current                                                                           |                          |       |        |       |      |

| 0.5 A                                                                                            |                          | -30   | _      | 30    |      |

| 1.0 A                                                                                            |                          | -19   | _      | 19    |      |

| 3.0 A                                                                                            |                          | -13.5 | _      | 13.5  |      |

| 3.7 A                                                                                            |                          | -12   | _      | 12    |      |

| 5.0 A                                                                                            |                          | -9.0  | _      | 9.0   |      |

| Current Sense Clamp Voltage                                                                      | V <sub>SENSE</sub>       |       |        |       | V    |

| I <sub>CNS</sub> = 15 mA Generated by the Device                                                 |                          | 4.5   | 6.0    | 7.0   |      |

| HS0 AND HS1 POWER OUTPUTS                                                                        |                          | -     |        |       |      |

| Drain-to-Source ON Resistance (I <sub>OUT</sub> = 5.5 A)                                         | R <sub>DS(ON)</sub>      |       |        |       | Ω    |

| $T_J = 25^{\circ}C$                                                                              |                          |       |        |       |      |

| V <sub>PWR</sub> = 6.0 V                                                                         |                          | _     | _      | 0.02  |      |

| V <sub>PWR</sub> = 9.0 V                                                                         |                          | _     | _      | 0.01  |      |

| V <sub>PWR</sub> = 13 V                                                                          |                          | _     | _      | 0.01  |      |

| $T_J = 150$ °C                                                                                   |                          |       |        |       |      |

| V <sub>PWR</sub> = 6.0 V                                                                         |                          | _     | _      | 0.034 |      |

|                                                                                                  |                          |       |        | 0.017 |      |

| V <sub>PWR</sub> = 9.0 V                                                                         |                          | _     | _      |       |      |

| V <sub>PWR</sub> = 13 V                                                                          |                          | _     | _      | 0.017 |      |

| Reverse Battery Source-to-Drain ON Resistance (I <sub>OUT</sub> = -5.5 A, T <sub>J</sub> = 25°C) | R <sub>DS(ON)REV</sub>   |       |        |       | Ω    |

| V <sub>PWR</sub> = -12 V                                                                         |                          | -     | _      | 0.02  |      |

| Output Self-Limiting Peak Current                                                                | I <sub>LIM(PK)</sub>     |       |        |       | Α    |

| Outputs ON, V <sub>OUT</sub> = V <sub>PWR</sub> -2.0 V                                           | (, 1.7)                  | 33    | 49     | 66    |      |

| Output Self-Limiting Sustain Current                                                             | I <sub>LIM(SUS)</sub>    |       |        |       | Α    |

| Outputs ON, V <sub>OUT</sub> = V <sub>PWR</sub> -2.0 V                                           | Liwi(303)                | 13    | 25     | 34    |      |

| Open Load Detection Current (Note 13)                                                            | I <sub>OLDC</sub>        | 30    | _      | 100   | μА   |

| Open Loud Detection Outlient (Note 10)                                                           | .OLDC                    | 1     | ĺ.     | .00   | μ, ( |

<sup>13.</sup> Output OFF Open Load Detection Current is the current required to flow through the load for the purpose of detecting the existence of an open load condition when the specific output is commanded OFF.

### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                               | Symbol                  | Min | Тур | Max | Unit |  |  |

|--------------------------------------------------------------|-------------------------|-----|-----|-----|------|--|--|

| HS0 AND HS1 POWER OUTPUTS (continued)                        |                         |     |     |     |      |  |  |

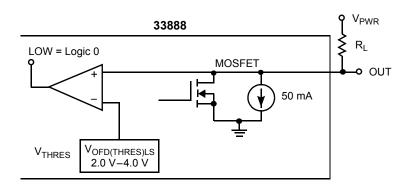

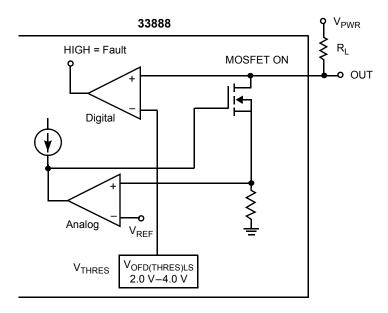

| Output Fault Detection Threshold (Note 14)                   | V <sub>OFD(THRES)</sub> |     |     |     | V    |  |  |

| Output Programmed OFF                                        |                         | 2.0 | 3.0 | 4.0 |      |  |  |

| Output Negative Clamp Voltage                                | $V_{CL}$                |     |     |     | V    |  |  |

| $0.5 \text{ A} \leq I_{OUT} \leq 2.0 \text{ A}$ , Output OFF |                         | -20 | _   | -   |      |  |  |

| Overtemperature Shutdown (Outputs OFF) (Note 15)             | T <sub>SD</sub>         | 160 | 175 | 190 | °C   |  |  |

| Overtemperature Shutdown Hysteresis (Note 15)                | T <sub>SD(HYS)</sub>    | 10  | _   | 30  | °C   |  |  |

| HS2 AND HS3 POWER OUTPUTS                                    |                         |     |     |     |      |  |  |

| Drain-to-Source ON Resistance (I <sub>OUT</sub> = 4.5 A)     | R <sub>DS(ON)</sub>     |     |     |     | Ω    |  |  |

| H32 AND H33 POWER OUTPUTS                                                                       |                         |     |     |       |    |

|-------------------------------------------------------------------------------------------------|-------------------------|-----|-----|-------|----|

| Drain-to-Source ON Resistance (I <sub>OUT</sub> = 4.5 A)                                        | R <sub>DS(ON)</sub>     |     |     |       | Ω  |

| $T_J = 25^{\circ}C$                                                                             |                         |     |     |       |    |

| V <sub>PWR</sub> = 6.0 V                                                                        |                         | -   | -   | 0.08  |    |

| V <sub>PWR</sub> = 9.0 V                                                                        |                         | _   | _   | 0.04  |    |

| V <sub>PWR</sub> = 13 V                                                                         |                         | _   | -   | 0.04  |    |

| $T_J = 150$ °C                                                                                  |                         |     |     |       |    |

| $V_{PWR} = 6.0 V$                                                                               |                         | _   | -   | 0.136 |    |

| V <sub>PWR</sub> = 9.0 V                                                                        |                         | _   | -   | 0.068 |    |

| V <sub>PWR</sub> = 13 V                                                                         |                         | _   | -   | 0.068 |    |

| Reverse Battery Source-to-Drain ON Resistance (I <sub>OUT</sub> = 4.5 A, T <sub>J</sub> = 25°C) | R <sub>DS(ON)REV</sub>  |     |     |       | Ω  |

| V <sub>PWR</sub> = -12 V                                                                        |                         | _   | _   | 0.08  |    |

| Output Self-Limiting Peak Current                                                               | I <sub>LIM(PK)</sub>    |     |     |       | Α  |

| Outputs ON, V <sub>OUT</sub> = V <sub>PWR</sub> -2.0 V                                          |                         | 15  | 23  | 35    |    |

| Output Self-Limiting Sustain Current                                                            | I <sub>LIM(SUS)</sub>   |     |     |       | Α  |

| Outputs ON, V <sub>OUT</sub> = V <sub>PWR</sub> -2.0 V                                          |                         | 6.0 | 10  | 15    |    |

| Open Load Detection Current (Note 16)                                                           | I <sub>OLDC</sub>       | 25  | -   | 100   | μА |

| Output Fault Detection Threshold (Note 17)                                                      | V <sub>OFD(THRES)</sub> |     |     |       | V  |

| Outputs Programmed OFF                                                                          |                         | 2.0 | 3.0 | 4.0   |    |

| Output Negative Clamp Voltage                                                                   | V <sub>CL</sub>         |     |     |       | V  |

| $0.5 \text{ A} \leq I_{OUT} \leq 2.0 \text{ A}$ , Outputs OFF                                   |                         | -20 | _   | _     |    |

| Overtemperature Shutdown (Outputs OFF) (Note 18)                                                | T <sub>SD</sub>         | 160 | 170 | 190   | °C |

| Overtemperature Shutdown Hysteresis (Note 18)                                                   | T <sub>SD(HYS)</sub>    | 10  | -   | 30    | °C |

|                                                                                                 |                         |     |     |       |    |

- 14. Output fault detection threshold with outputs programmed OFF. For the Low-Side Outputs, fault detection thresholds are the same for output open and battery shorts.

- 15. Guaranteed by design. Not production tested.

- 16. Output OFF Open Load Detection Current is the current required to flow through the load for the purpose of detecting the existence of an open load condition when the specific output is commanded OFF.

- 17. Output fault detection threshold with outputs programmed OFF.

- 18. Guaranteed by design. Not production tested.

### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions  $6.0 \text{ V} \le \text{V}_{PWR} \le 27 \text{ V}, 4.5 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}, -40^{\circ}\text{C} \le \text{T}_{J} \le 150^{\circ}\text{C}$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $\text{T}_{A}$  = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                 | Symbol                  | Min | Тур | Max | Unit |  |  |  |  |

|--------------------------------------------------------------------------------|-------------------------|-----|-----|-----|------|--|--|--|--|

| LOW-SIDE POWER OUTPUTS                                                         |                         |     |     |     |      |  |  |  |  |

| Drain-to-Source ON Resistance (I <sub>OUT</sub> = 0.3 A)                       | R <sub>DS(ON)</sub>     |     |     |     | Ω    |  |  |  |  |

| $T_J = 25$ °C                                                                  |                         |     |     |     |      |  |  |  |  |

| V <sub>PWR</sub> = 4.5 V; V <sub>DD</sub> = 3.5 V, 33888A Only                 |                         | _   | _   | 8.0 |      |  |  |  |  |

| V <sub>PWR</sub> = 6.0 V                                                       |                         | _   | _   | 1.0 |      |  |  |  |  |

| V <sub>PWR</sub> = 9.0 V                                                       |                         | _   | _   | 0.7 |      |  |  |  |  |

| V <sub>PWR</sub> = 13 V                                                        |                         | _   | _   | 0.6 |      |  |  |  |  |

| $T_{J} = 150^{\circ}C$                                                         |                         |     |     |     |      |  |  |  |  |

| V <sub>PWR</sub> = 4.5 V; V <sub>DD</sub> = 3.5 V, 33888A Only                 |                         | _   | _   | 8.0 |      |  |  |  |  |

| V <sub>PWR</sub> = 6.0 V                                                       |                         | _   | _   | 1.8 |      |  |  |  |  |

| V <sub>PWR</sub> = 9.0 V                                                       |                         | _   | _   | 1.1 |      |  |  |  |  |

| V <sub>PWR</sub> = 13 V                                                        |                         | _   | _   | 0.9 |      |  |  |  |  |

| Output Self-Limiting Current (Outputs Programmed ON, V <sub>OUT</sub> = 3.0 V) | I <sub>LIM</sub>        |     |     |     | Α    |  |  |  |  |

| Low-Side 4, 6, 8, 10                                                           |                         | 0.5 | 0.9 | 1.5 |      |  |  |  |  |

| Low-Side 5, 7, 9, 11                                                           |                         | 0.8 | 1.3 | 2.0 |      |  |  |  |  |

| Output OFF Open Load Detection Current (Note 19)                               | I <sub>OLDC</sub>       |     |     |     | μА   |  |  |  |  |

| Output Programmed OFF, V <sub>OUT</sub> = 3.0 V                                |                         | 25  | 50  | 100 |      |  |  |  |  |

| Output Fault Detection Threshold (Note 20)                                     | V <sub>OFD(THRES)</sub> |     |     |     | V    |  |  |  |  |

| Output Programmed OFF                                                          | , ,                     | 2.0 | 3.0 | 4.0 |      |  |  |  |  |

| Output Clamp Voltage                                                           | V <sub>CL</sub>         |     |     |     | V    |  |  |  |  |

| $2.0 \text{ mA} \le I_{OUT} \le 200 \text{ mA}$ , Outputs OFF                  |                         | 41  | 53  | 60  |      |  |  |  |  |

| Low-Side Body Diode Voltage (I = -300 mA, T <sub>J</sub> = 125°C)              | V <sub>BD</sub>         | 0.5 | 0.7 | 0.9 | V    |  |  |  |  |

| Overtemperature Shutdown (Outputs OFF) (Note 21)                               | T <sub>LIM</sub>        | 160 | 170 | 190 | °C   |  |  |  |  |

| Overtemperature Shutdown Hysteresis (Note 21)                                  | T <sub>LIM(HYS)</sub>   | 10  | 20  | 30  | °C   |  |  |  |  |

- Output OFF Open Load Detection Current is the current required to flow through the load for the purpose of detecting the existence of an open load condition when the specific output is commanded OFF.

- Output fault detection threshold with outputs programmed OFF. For the low-side outputs, fault detection thresholds are the same for output

open and battery shorts.

- 21. Guaranteed by design. Not production tested.

### STATIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                          | Symbol               | Min                 | Тур | Max  | Unit |

|---------------------------------------------------------------------------------------------------------|----------------------|---------------------|-----|------|------|

| CONTROL INTERFACE                                                                                       |                      | •                   |     | •    |      |

| Input Logic High Voltage (Note 22)                                                                      | V <sub>IH</sub>      | 0.7 V <sub>DD</sub> | _   | _    | V    |

| Input Logic Low Voltage (Note 22)                                                                       | V <sub>IL</sub>      | -                   | -   | 1.0  | V    |

| Input Logic Voltage Hysteresis (SI, $\overline{\text{CS}}$ , SCLK, IHS[0:3], ILS) (Note 23)             | V <sub>IN(HYS)</sub> | 100                 | 350 | 750  | mV   |

| Input Logic Pulldown Current (SI, SCLK, IHS[0:3], ILS, WDIN)                                            | I <sub>DWN</sub>     | 5.0                 | -   | 20   | μА   |

| Input Logic Pulldown Resistor (WAKE, RST)                                                               | R <sub>DWN</sub>     | 100                 | 200 | 400  | kΩ   |

| Input Logic Pullup Current ( $\overline{\text{CS}}$ , V <sub>IN</sub> = 0.7 V <sub>DD</sub> ) (Note 24) | I <sub>UPC</sub>     | 5.0                 | _   | 20   | μА   |

| Input Logic Pullup Current (FSI, V <sub>IN</sub> = 3.5 V)                                               | l <sub>UPF</sub>     | 5.0                 | -   | 20   | μА   |

| Wake Input Clamp Voltage (I <sub>WICI</sub> < 2.5 mA) (Note 25)                                         | V <sub>WIC</sub>     | 7.0                 | _   | 14   | V    |

| Wake Input Forward Voltage (I <sub>WICI</sub> = -2.5 mA)                                                | V <sub>WIF</sub>     | -2.0                | -   | -0.3 | V    |

| SO High-State Output Voltage (I <sub>OH</sub> = 1.0 mA)                                                 | V <sub>SOH</sub>     | 0.8 V <sub>DD</sub> | _   | -    | V    |

| FS, SO Low-State Output Voltage (I <sub>OL</sub> = -1.6 mA)                                             | V <sub>SOL</sub>     | _                   | 0.2 | 0.4  | V    |

| SO Tri-State Leakage Current ( $\overline{\text{CS}} \ge 3.5 \text{ V}$ )                               | I <sub>SOLK</sub>    | -5.0                | 0   | 5.0  | μА   |

| Input Capacitance (Note 26)                                                                             | C <sub>IN</sub>      | _                   | 4.0 | 12   | pF   |

| SO, FS Tri-State Capacitance (Note 23)                                                                  | C <sub>SO</sub>      | _                   | _   | 20   | pF   |

- 22. Upper and lower logic threshold voltage range applies to SI,  $\overline{\text{CS}}$ , SCLK,  $\overline{\text{RST}}$ , IHS[0:3], ILS, WAKE, and WDIN input signals. The WAKE, FSI, and  $\overline{\text{RST}}$  signals are derived from an internal supply.

- 23. Parameter is guaranteed by design but is not production tested.

- 24. CS is pulled up to V<sub>DD</sub>.

- 25. The current must be limited by a series resistor when using voltages higher than the W<sub>ICV</sub>.

- 26. Input capacitance of SI,  $\overline{\text{CS}}$ , SCLK,  $\overline{\text{RST}}$ , IHS[0:3], ILS, WAKE, and WDIN. This parameter is guaranteed by process monitoring but is not production tested.

#### **DYNAMIC ELECTRICAL CHARACTERISTICS**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                    | Symbol                | Min  | Тур  | Max  | Unit |

|---------------------------------------------------|-----------------------|------|------|------|------|

| POWER OUTPUT TIMING                               |                       |      |      |      |      |

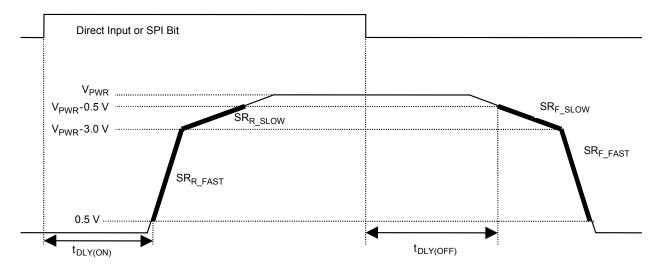

| High-Side Output Rising Fast Slew Rate (Note 27)  | SR <sub>R_FAST</sub>  |      |      |      | V/μs |

| 6.0 V < V <sub>PWR</sub> < 9.0 V                  |                       | 0.03 | _    | 0.6  |      |

| 9.0 V < V <sub>PWR</sub> < 16 V                   |                       | 0.05 | 0.5  | 0.8  |      |

| 16 V < V <sub>PWR</sub> < 27 V                    |                       | 0.1  | _    | 1.1  |      |

| High-Side Output Rising Slow Slew Rate (Note 28)  | SR <sub>R_SLOW</sub>  |      |      |      | V/μs |

| 6.0 V < V <sub>PWR</sub> < 9.0 V                  |                       | 0.01 | -    | 0.14 |      |

| 9.0 V < V <sub>PWR</sub> < 16 V                   |                       | 0.01 | 0.08 | 0.18 |      |

| 16 V < V <sub>PWR</sub> < 27 V                    |                       | 0.01 | _    | 0.2  |      |

| High-Side Output Falling Fast Slew Rate (Note 27) | SR <sub>F_FAST</sub>  |      |      |      | V/μs |

| 6.0 V < V <sub>PWR</sub> < 9.0 V                  |                       | 0.2  | -    | 1.0  |      |

| 9.0 V < V <sub>PWR</sub> < 16 V                   |                       | 0.3  | 8.0  | 1.5  |      |

| 16 V < V <sub>PWR</sub> < 27 V                    |                       | 0.5  | -    | 2.2  |      |

| High-Side Output Falling Slow Slew Rate (Note 28) | SR <sub>F_SLOW</sub>  |      |      |      | V/μs |

| 6.0 V < V <sub>PWR</sub> < 9.0 V                  |                       | 0.05 | -    | 0.3  |      |

| 9.0 V < V <sub>PWR</sub> < 16 V                   |                       | 0.08 | 0.15 | 0.4  |      |

| 16 V < V <sub>PWR</sub> < 27 V                    |                       | 0.08 | -    | 0.5  |      |

| High-Side Output Turn ON Delay Time (Note 29)     | t <sub>DLY(ON)</sub>  | 5.0  | 30   | 150  | μS   |

| High-Side Output Turn OFF Delay Time (Note 30)    | t <sub>DLY(OFF)</sub> | 5.0  | 80   | 150  | μS   |

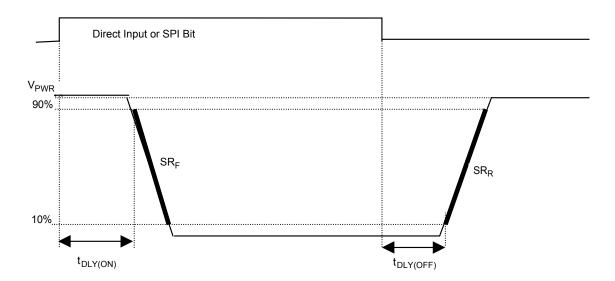

| Low-Side Output Falling Slew Rate (Note 31)       | SR <sub>F</sub>       | 0.5  | 3.0  | 10   | V/μs |

| Low-Side Output Rising Slew Rate (Note 31)        | SR <sub>R</sub>       | 1.0  | 6.0  | 20   | V/μs |

| Low-Side Output Turn ON Delay Time (Note 32)      | t <sub>DLY(ON)</sub>  | 0.5  | 2.0  | 10   | μS   |

| Low-Side Output Turn OFF Delay Time (Note 33)     | t <sub>DLY(OFF)</sub> | 0.5  | 4.0  | 10   | μS   |

| Low-Side Output Fault Delay Timer (Note 34)       | t <sub>DLY(FS)</sub>  | 70   | 150  | 250  | μS   |

| Watchdog Timeout (Note 35)                        | t <sub>WDTO</sub>     | 340  | 584  | 770  | ms   |

- 27. High-side output rise and fall fast slew rates measured across a 5.0  $\Omega$  resistive load at high-side output = 0.5 V to V<sub>PWR</sub>-3.0 V (see <u>Figure 2</u>, page 18). These parameters are guaranteed by process monitoring.

- 28. High-side output rise and fall slow slew rates measured across a 5.0  $\Omega$  resistive load at high-side output = 0.5 V to V<sub>PWR</sub>-3.0 V (see <u>Figure 2</u>, page 18). These parameters are guaranteed by process monitoring.

- 29. High-side output turn-ON delay time measured from 50% of the rising IHS to 0.5 V of output OFF with  $R_L$  = 27  $\Omega$  resistive load (see <u>Figure 2</u>, page 18).

- 30. High-side output turn-OFF delay time measured from 50% of the falling IHS to  $V_{PWR}$ -2.0 V of the output OFF with  $R_L$  = 27  $\Omega$  resistive load (see Figure 2, page 18).

- 31. Low-side output rise and fall slew rates measured across a 5.0 Ω resistive load at low-side output = 10% to 90% (see Figure 3, page 18).

- 32. Low-side output turn-ON delay time measured from 50% of the rising ILS to 90% of V<sub>OUT</sub> with R<sub>L</sub> = 27 Ω resistive load (see <u>Figure 3</u>, page 18)

- 33. Low-side output turn-OFF delay time measured from 50% of the falling ILS to 10% of  $V_{OUT}$  with  $R_L$  = 27  $\Omega$  resistive load (see <u>Figure 3</u>, page 18). These parameters are guaranteed by process monitoring.

- 34. Propagation time of Short Fault Disable Report Delay measured from rising edge of  $\overline{\text{CS}}$  to output disabled, low-side = 5.0 V, and device configured for low-side output overcurrent latchoff using CLOCCR.

- 35. Watchdog timeout delay is measured from the rising edge of WAKE or RST from the sleep state to the HS[0:1] turn-ON with the outputs driven OFF and the FSI floating. The accuracy of two of

### **DYNAMIC ELECTRICAL CHARACTERISTICS (continued)**

Characteristics noted under conditions 6.0 V  $\leq$  V<sub>PWR</sub>  $\leq$  27 V, 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V, -40°C  $\leq$  T<sub>J</sub>  $\leq$  150°C unless otherwise noted. Typical values noted reflect the approximate parameter mean at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                  | Symbol                | Min | Тур | Max | Unit |

|-----------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|------|

| POWER OUTPUT TIMING (continued)                                                                                 |                       |     |     |     |      |

| Peak Current Limit Timer (Note 36)                                                                              | t <sub>PCT</sub>      | 40  | 70  | 100 | ms   |

| Direct Input Switching Frequency (Note 37)                                                                      | f <sub>PWM</sub>      | -   | 125 | _   | Hz   |

| SPI INTERFACE TIMING (Note 38)                                                                                  |                       | l   | •   |     |      |

| Recommended Frequency of SPI Operation                                                                          | f <sub>SPI</sub>      |     |     |     | MHz  |

| Normal Mode                                                                                                     |                       | _   | _   | 3.0 |      |

| Extended Mode: V <sub>DD</sub> = 3.4 V; V <sub>PWR</sub> = 4.5 V, APNB Suffix Only                              |                       | _   | _   | 2.1 |      |

| Required Low State Duration for RST (Note 39)                                                                   | t <sub>WRST</sub>     | _   | 50  | 167 | ns   |

| Rising Edge of $\overline{\text{CS}}$ to Falling Edge of $\overline{\text{CS}}$ (Required Setup Time) (Note 40) | t <sub>cs</sub>       | -   | _   | 300 | ns   |

| Rising Edge of RST to Falling Edge of CS (Required Setup Time) (Note 40)                                        | t <sub>ENBL</sub>     | -   | _   | 5.0 | μS   |

| Falling Edge of $\overline{\text{CS}}$ to Rising Edge of SCLK (Required Setup Time) (Note 40)                   | t <sub>LEAD</sub>     | -   | 50  | 167 | ns   |

| Required High State Duration of SCLK (Required Setup Time) (Note 40)                                            | t <sub>WSCLKh</sub>   | -   | -   | 167 | ns   |

| Required Low State Duration of SCLK (Required Setup Time) (Note 40)                                             | t <sub>WSCLKI</sub>   | -   | -   | 167 | ns   |

| Falling Edge of SCLK to Rising Edge of $\overline{\text{CS}}$ (Required Setup Time) (Note 40)                   | t <sub>LAG</sub>      | -   | 50  | 167 | ns   |

| SI to Falling Edge of SCLK (Required Setup Time) (Note 40)                                                      | t <sub>SI(SU)</sub>   | -   | 25  | 83  | ns   |

| Falling Edge of SCLK to SI (Required Hold Time) (Note 40)                                                       | t <sub>SI(HOLD)</sub> | -   | 25  | 83  | ns   |

| SO Rise Time                                                                                                    | t <sub>RSO</sub>      |     |     |     | ns   |