### Multi-mode controller for SMPS

### **Features**

- Selectable multi-mode operation: fixed frequency or quasi-resonant

- On-board 700 V high-voltage start-up

- Advanced light load management

- Low quiescent current (< 3 mA)

- Adaptive UVLO

- Line feedforward for constant power capability vs. mains voltage

- Pulse-by-pulse OCP, shutdown on overload (latched or autorestart)

- Transformer saturation detection

- Programmable frequency modulation for EMI reduction

- Latched or autorestart OVP

- Brownout protection

- -600/+800 mA totem pole gate driver with active pull-down during UVLO

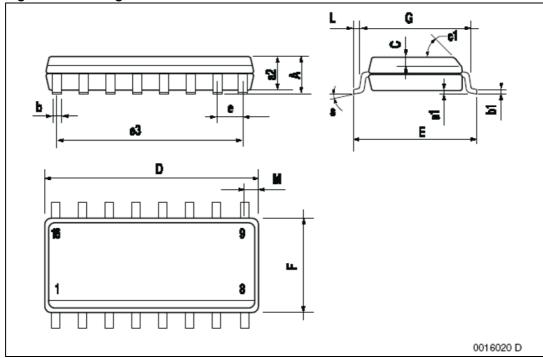

- SO16N package

### **Applications**

- Hi-end AC-DC adapter/charger

- LCD TV/monitor, PDP

- digital consumer, IT equipment

- single-stage PFC

Contents L6566B

## **Contents**

| 1 | Desc  | eription                                                      | 6  |

|---|-------|---------------------------------------------------------------|----|

| 2 | Pin s | settings                                                      | 8  |

|   | 2.1   | Connections                                                   | 8  |

|   | 2.2   | Pin description                                               | 8  |

| 3 | Elect | trical data                                                   | 11 |

|   | 3.1   | Maximum rating                                                | 11 |

|   | 3.2   | Thermal data                                                  | 11 |

| 4 | Elect | trical characteristics                                        | 12 |

| 5 | Appl  | ication information                                           | 17 |

|   | 5.1   | High-voltage start-up generator                               | 18 |

|   | 5.2   | Zero current detection and triggering block; oscillator block | 21 |

|   | 5.3   | Burst-mode operation at no load or very light load            | 24 |

|   | 5.4   | Adaptive UVLO                                                 | 25 |

|   | 5.5   | PWM control block                                             | 26 |

|   | 5.6   | PWM comparator, PWM latch and voltage feedforward blocks      | 27 |

|   | 5.7   | Hiccup-mode OCP                                               | 30 |

|   | 5.8   | Frequency modulation                                          | 31 |

|   | 5.9   | Latched disable function                                      | 32 |

|   | 5.10  | Soft-start and delayed latched shutdown upon overcurrent      | 33 |

|   | 5.11  | OVP block                                                     | 35 |

|   | 5.12  | Brownout protection                                           | 37 |

|   | 5.13  | Slope compensation                                            | 40 |

|   | 5.14  | Summary of L6566B power management functions                  | 41 |

|   |                                | Contents |

|---|--------------------------------|----------|

| 6 | Application examples and ideas | 44       |

| 7 | Package mechanical data        | 47       |

| 8 | Order codes                    | 49       |

| 9 | Revision history               | 50       |

List of tables L6566B

## List of tables

| Table 2.  | Pin functions                                                 | 8  |

|-----------|---------------------------------------------------------------|----|

| Table 3.  | Absolute maximum ratings                                      | 11 |

| Table 4.  | Thermal data                                                  | 11 |

| Table 5.  | Electrical characteristics                                    | 12 |

| Table 6.  | L6566B light load management features                         | 41 |

| Table 7.  | L6566B protections                                            | 42 |

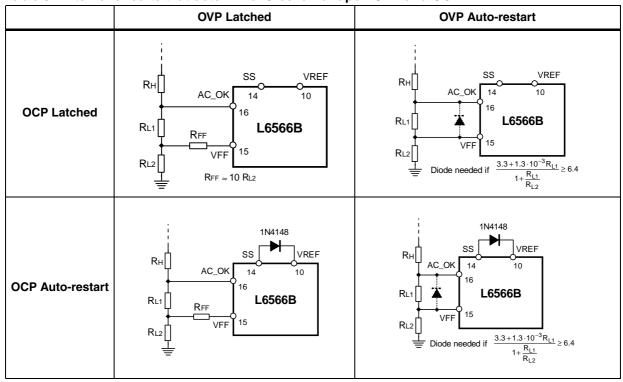

| Table 8.  | External circuits that determine IC behavior upon OVP and OCP | 45 |

| Table 9.  | SO16N mechanical data                                         | 48 |

| Table 10. | Order codes                                                   | 49 |

| Table 11. | Revision history                                              | 50 |

L6566B List of figures

# List of figures

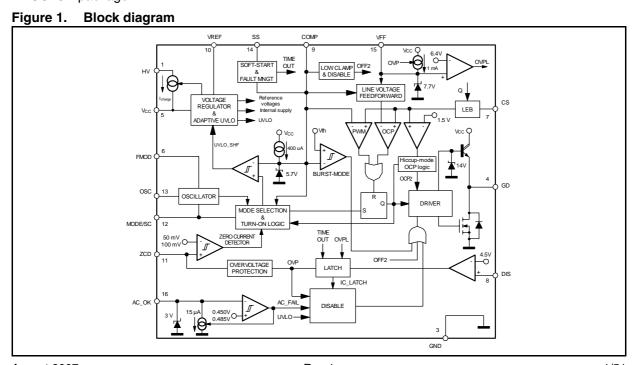

| Figure 1.  | Block diagram                                                                        | 1    |

|------------|--------------------------------------------------------------------------------------|------|

| igure 2.   | Typical system block diagram                                                         | 7    |

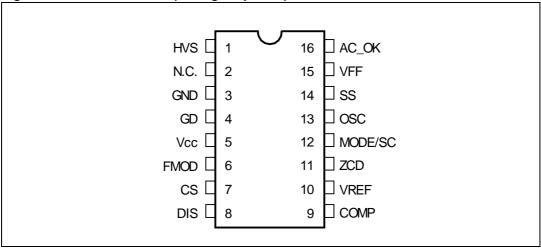

| igure 3.   | Pin connection (through top view)                                                    | 8    |

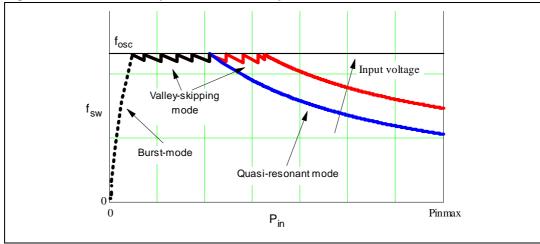

| igure 4.   | Multi-mode operation with QR option active                                           | . 17 |

| igure 5.   | High-voltage start-up generator: internal schematic                                  | . 18 |

| igure 6.   | Timing diagram: normal power-up and power-down sequences                             | . 19 |

| igure 7.   | Timing diagram showing short-circuit behavior (SS pin clamped at 5V)                 |      |

| igure 8.   | Zero current detection block, triggering block, oscillator block and related logic   | . 20 |

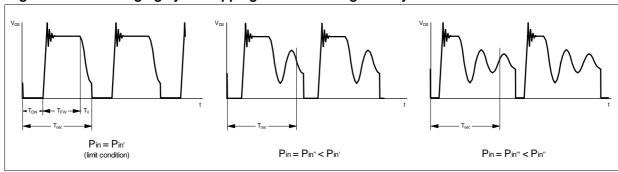

| igure 9.   | Drain ringing cycle skipping as the load is gradually reduced                        |      |

| igure 10.  | Operation of ZCD, triggering and oscillator blocks (QR option active)                | . 23 |

| Figure 11. | Load-dependent operating modes: timing diagrams                                      | . 24 |

| Figure 12. | Addition of an offset to the current sense lowers the burst-mode operation threshold | . 25 |

| Figure 13. | Adaptive UVLO block                                                                  |      |

| Figure 14. | Possible feedback configurations that can be used with the L6566B                    | . 26 |

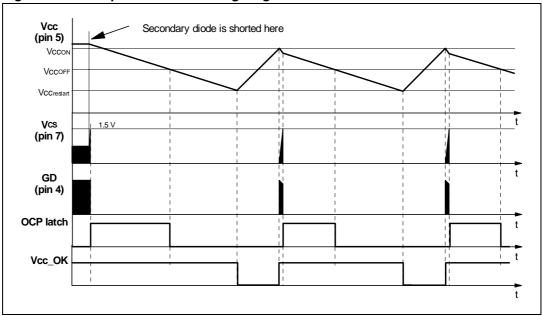

| Figure 15. | Externally controlled burst-mode operation by driving pin COMP: timing diagram       | . 27 |

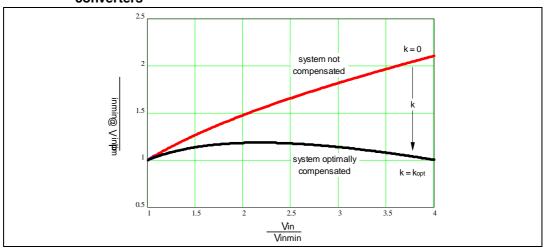

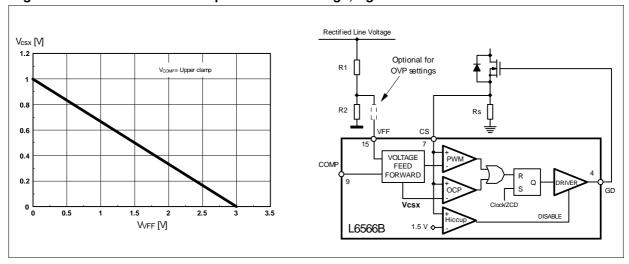

| igure 16.  | Typical power capability change vs. input voltage in QR flyback converters           |      |

| igure 17.  | Left: Overcurrent setpoint vs. VFF voltage; right: Line Feedforward function block   |      |

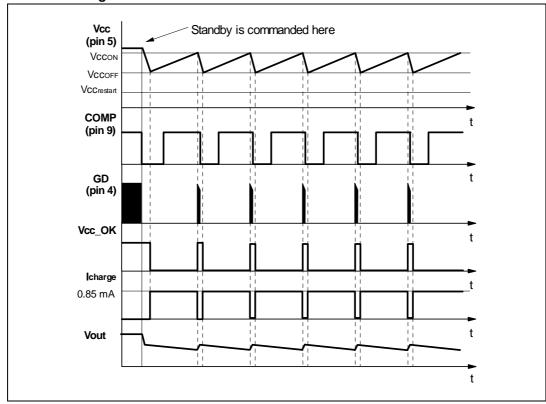

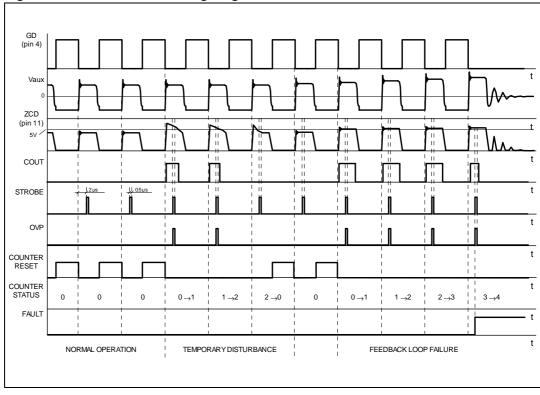

| Figure 18. | Hiccup-mode OCP: timing diagram                                                      |      |

| Figure 19. | Frequency modulation circuit                                                         |      |

| igure 20.  | Operation after latched disable activation: timing diagram                           |      |

| Figure 21. | Soft-start pin operation under different operating conditions and settings           |      |

| igure 22.  | OVP Function: internal block diagram                                                 |      |

| igure 23.  | OVP function: timing diagram                                                         |      |

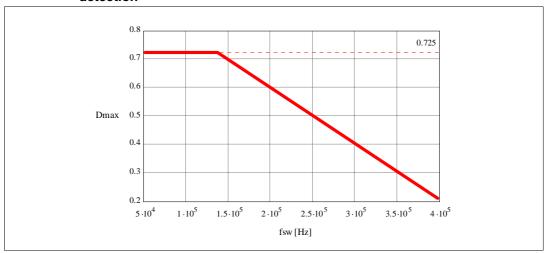

| igure 24.  | Maximum allowed duty cycle vs. switching frequency for correct OVP detection         |      |

| igure 25.  | Brownout protection: internal block diagram and timing diagram                       |      |

| igure 26.  | Voltage sensing techniques to implement brownout protection with the L6566B          |      |

| igure 27.  | Slope compensation waveforms                                                         |      |

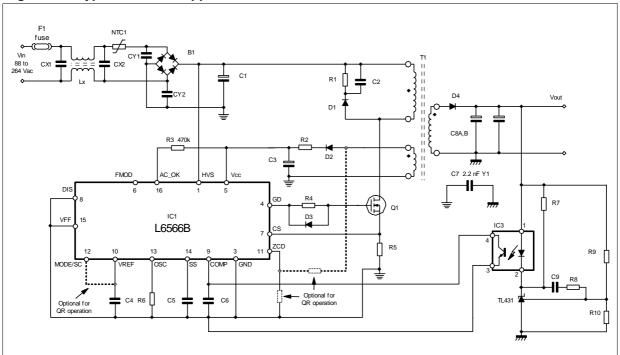

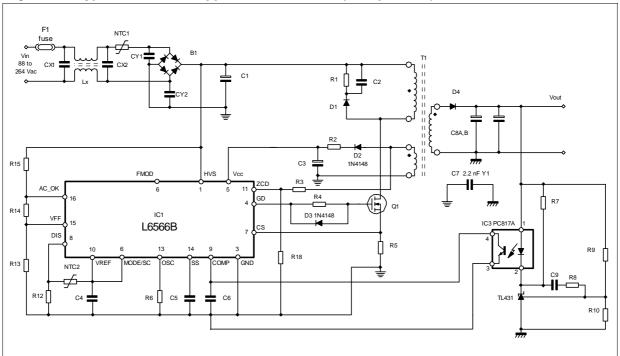

| igure 28.  | Typical low-cost application schematic                                               |      |

| igure 29.  | Typical full-feature application schematic (QR operation)                            |      |

| igure 30.  | Typical full-feature application schematic (FF operation)                            |      |

| igure 31.  | Frequency foldback at light load (FF operation)                                      |      |

| igure 32.  | Latched shutdown upon mains overvoltage                                              | . 46 |

5/

Description L6566B

### 1 Description

The L6566B is an extremely versatile current-mode primary controller ICs, specifically designed for high-performance offline flyback converters. It is also suited for single-stage single-switch input-current-shaping converters (single-stage PFC) for applications supposed to comply with EN61000-3-2 or JEITA-MITI regulations.

Both Fixed-frequency (FF) and Quasi-resonant (QR) operation are supported. The user can pick either of the two depending on application needs. The device features an externally programmable oscillator: it defines converter's switching frequency in FF mode and the maximum allowed switching frequency in QR mode.

When FF operation is selected, the ICs work like a standard current-mode controller with a maximum duty cycle limited at 70% min. The oscillator frequency can be modulated to mitigate EMI emissions.

QR operation, when selected, occurs at heavy load and is achieved through a transformer demagnetization sensing input that triggers MOSFET's turn-on. Under some conditions, ZVS (Zero-voltage Switching) can be achieved. Converter's power capability rise with the mains voltage is compensated by line voltage feedforward. At medium and light load, as the QR operating frequency equals the oscillator frequency, a function (valley skipping) is activated to prevent further frequency rise and keep the operation as close to ZVS as possible.

With either FF or QR operation, at very light load the ICs enter a controlled burst-mode operation that, along with the built-in non-dissipative high-voltage start-up circuit and the low quiescent current, helps keep low the consumption from the mains and meet energy saving recommendations.

An innovative adaptive UVLO helps minimize the issues related to the fluctuations of the self-supply voltage due to transformer's parasitics.

The protection functions included in this device are: not-latched input undervoltage (brownout), output OVP (auto-restart or latch-mode selectable), a first-level OCP with delayed shutdown to protect the system during overload or short circuit conditions (auto-restart or latch-mode selectable) and a second-level OCP that is invoked when the transformer saturates or the secondary diode fails short. A latched disable input allows easy implementation of OTP with an external NTC, while an internal thermal shutdown prevents IC overheating.

Programmable soft-start, leading-edge blanking on the current sense input for greater noise immunity, slope compensation (in FF mode only), and a shutdown function for externally controlled burst-mode operation or remote ON/OFF control complete the equipment of this device.

L6566B Description

FLYBACK DC-DC CONVERTER

Rectified & Filtered Mains Voltage

L6566B

Figure 2. Typical system block diagram

**47/**

Pin settings L6566B

## 2 Pin settings

### 2.1 Connections

Figure 3. Pin connection (through top view)

## 2.2 Pin description

**Table 2. Pin functions**

| N° | Pin  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | HVS  | High-voltage start-up. The pin, able to withstand 700V, is to be tied directly to the rectified mains voltage. A 1 mA internal current source charges the capacitor connected between Vcc pin (5) and GND pin (3) until the voltage on the Vcc pin reaches the turn-on threshold, then it is shut down. Normally, the generator is reenabled when the Vcc voltage falls below 5V to ensure a low power throughput during short circuit. Otherwise, when a latched protection is tripped the generator is re-enabled 0.5V below the turn-on threshold, to keep the latch supplied; or, when the IC is turned off by pin COMP (9) pulled low the generator is active just below the UVLO threshold to allow a faster restart. |

| 2  | N.C. | Not internally connected. Provision for clearance on the PCB to meet safety requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3  | GND  | Ground. Current return for both the signal part of the IC and the gate drive. All of the ground connections of the bias components should be tied to a track going to this pin and kept separate from any pulsed current return.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4  | GD   | Gate driver output. The totem pole output stage is able to drive power MOSFET's and IGBT's with a peak current capability of 800 mA source/sink.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

L6566B Pin settings

Table 2. Pin functions (continued)

| N° | Pin  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5  | Vcc  | Supply Voltage of both the signal part of the IC and the gate driver. The internal high voltage generator charges an electrolytic capacitor connected between this pin and GND (pin 3) as long as the voltage on the pin is below the turn-on threshold of the IC, after that it is disabled and the chip is turned on. The IC is disabled as the voltage on the pin falls below the UVLO threshold. This threshold is reduced at light load to counteract the natural reduction of the self-supply voltage. Sometimes a small bypass capacitor (0.1 $\mu F$ typ.) to GND might be useful to get a clean bias voltage for the signal part of the IC.                                                               |

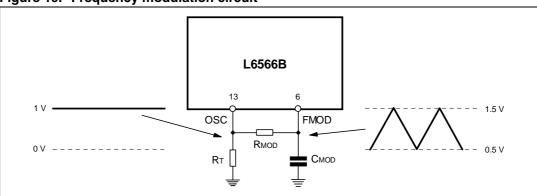

| 6  | FMOD | Frequency modulation input. When FF mode operation is selected, a capacitor connected from this pin to GND (pin 3) is alternately charged and discharged by internal current sources. As a result, the voltage on the pin is a symmetrical triangular waveform with the frequency related to the capacitance value. By connecting a resistor from this pin to pin 13 (OSC) it is possible to modulate the current sourced by the OSC pin and then the oscillator frequency. This modulation is to reduce the peak value of EMI emissions by means of a spread-spectrum action. If the function is not used, the pin will be left open.                                                                             |

| 7  | CS   | Input to the PWM comparator. The current flowing in the MOSFET is sensed through a resistor, the resulting voltage is applied to this pin and compared with an internal reference to determine MOSFET's turn-off. The pin is equipped with 150 ns min. blanking time after the gate-drive output goes high for improved noise immunity. A second comparison level located at 1.5V latches the device off and reduces its consumption in case of transformer saturation or secondary diode short circuit. The information is latched until the voltage on the Vcc pin (5) goes below the UVLO threshold, hence resulting in intermittent operation. A logic circuit improves sensitivity to temporary disturbances. |

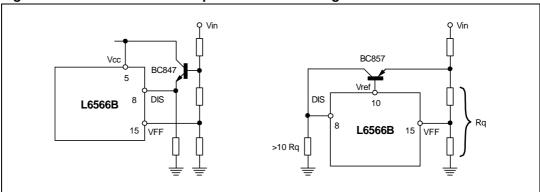

| 8  | DIS  | IC's latched disable input. Internally the pin connects a comparator that, when the voltage on the pin exceeds 4.5V, latches off the IC and brings its consumption to a lower value. The latch is cleared as the voltage on the Vcc pin (5) goes below the UVLO threshold, but the HV generator keeps the Vcc voltage high (see pin 1 description). It is then necessary to recycle the input power to restart the IC. For a quick restart pull pin 16 (AC_OK) below the disable threshold (see pin 16 description). Bypass the pin with a capacitor to GND (pin 3) to reduce noise pickup. Ground the pin if the function is not used.                                                                            |

| 9  | COMP | Control input for loop regulation. The pin will be driven by the phototransistor (emitter-grounded) of an optocoupler to modulate its voltage by modulating the current sunk. A capacitor placed between the pin and GND (3), as close to the IC as possible to reduce noise pick-up, sets a pole in the output-to-control transfer function. The dynamics of the pin is in the 2.5 to 5V range. A voltage below an internally defined threshold activates burst-mode operation. The voltage at the pin is bottom-clamped at about 2V. If the clamp is externally overridden and the voltage is pulled below 1.4V the IC will shut down.                                                                           |

| 10 | VREF | An internal generator furnishes an accurate voltage reference (5V±2%) that can be used to supply few mA to an external circuit. A small film capacitor (0.1 $\mu F$ typ.), connected between this pin and GND (3), is recommended to ensure the stability of the generator and to prevent noise from affecting the reference. This reference is internally monitored by a separate auxiliary reference and any failure or drift will cause the IC to latch off.                                                                                                                                                                                                                                                    |

Pin settings L6566B

Table 2. Pin functions (continued)

| N° | Pin     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | ZCD     | Transformer demagnetization sensing input for quasi-resonant operation and OVP input. The pin is externally connected to the transformer's auxiliary winding through a resistor divider. A negative-going edge triggers MOSFET's turn-on if QR mode is selected.  A voltage exceeding 5V shuts the IC down and brings its consumption to a lower value (OVP). Latch-off or auto-restart mode is selectable externally. This function is strobed and digitally filtered to increase noise immunity.                                                                                                                                                                                                                     |

| 12 | MODE/SC | Operating mode selection. If the pin is connected to the VREF pin (7) Quasi-resonant operation is selected, the oscillator (pin 13, OSC) determines the maximum allowed operating frequency.  Fixed-frequency operation is selected if the pin is not tied to VREF, in which case the oscillator determines the actual operating frequency, the maximum allowed duty cycle is set at 70% min. and the pin delivers a voltage ramp synchronized to the oscillator when the gate-drive output is high; the voltage delivered is zero while the gate-drive output is low. The pin is to be connected to pin CS (7) via a resistor for slope compensation.                                                                 |

| 13 | OSC     | Oscillator pin. The pin is an accurate 1 V voltage source, and a resistor connected from the pin to GND (pin 3) defines a current. This current is internally used to set the oscillator frequency that defines the maximum allowed switching frequency of the L6566B, if working in QR mode, or the operating switching frequency if working in FF mode.                                                                                                                                                                                                                                                                                                                                                              |

| 14 | SS      | Soft-start current source. At start-up a capacitor Css between this pin and GND (pin 3) is charged with an internal current generator. During the ramp, the internal reference clamp on the current sense pin (7, CS) rises linearly starting from zero to its final value, thus causing the duty cycle to increase progressively starting from zero as well. During soft-start the Adaptive UVLO function and all functions monitoring pin COMP are disabled. The soft-start capacitor is discharged whenever the supply voltage of the IC falls below the UVLO threshold. The same capacitor is used to delay IC's shutdown (latch-off or auto-restart mode selectable) after detecting an overload condition (OLP). |

| 15 | VFF     | Line voltage feedforward input. The information on the converter's input voltage is fed into the pin through a resistor divider and is used to change the setpoint of the pulse-by-pulse current limitation (the higher the voltage, the lower the setpoint). The linear dynamics of the pin ranges from 0 to 3V. A voltage higher than 3V makes the IC stop switching. If feedforward is not desired, tie the pin to GND (pin 3) directly if a latch-mode OVP is not required (see pin 11, ZCD) or through a $10k\Omega$ min. resistor if a latch-mode OVP is required. Bypass the pin with a capacitor to GND (pin 3) to reduce noise pick-up.                                                                       |

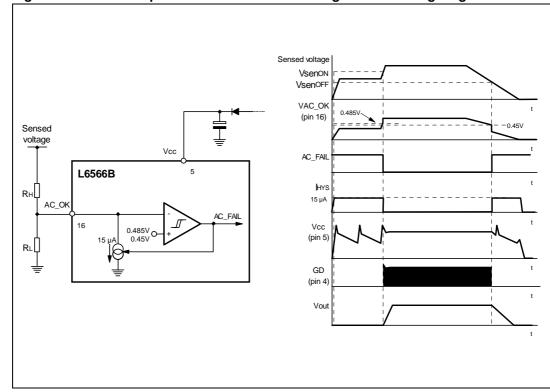

| 16 | AC_OK   | Brownout protection input. A voltage below 0.45V shuts down (not latched) the IC, lowers its consumption and clears the latch set by latched protections (DIS>4.5V, SS>6.4V, VFF>6.4V). IC's operation is re-enabled as the voltage exceeds 0.45V. The comparator is provided with current hysteresis: an internal 15 $\mu$ A current generator is ON as long as the voltage on the pin is below 0.45V and is OFF if this value is exceeded. Bypass the pin with a capacitor to GND (pin 3) to reduce noise pick-up. Tie to Vcc with a 220 to 680 k $\Omega$ resistor if the function is not used.                                                                                                                     |

L6566B Electrical data

## 3 Electrical data

## 3.1 Maximum rating

Table 3. Absolute maximum ratings

| Symbol Pin           |              | Parameter                                | Value        | Unit |

|----------------------|--------------|------------------------------------------|--------------|------|

| V <sub>HVS</sub>     | 1            | Voltage range (referred to ground)       | -0.3 to 700  | V    |

| I <sub>HVS</sub>     | 1            | Output current                           | Self-limited |      |

| V <sub>CC</sub>      | 5            | IC supply voltage (Icc = 20 mA)          | Self-limited |      |

| V <sub>FMOD</sub>    | 6            | Voltage range                            | -0.3 to 2    | V    |

| V <sub>max</sub>     | 7, 8, 10, 14 | Analog inputs & outputs                  | -0.3 to 7    | V    |

| V <sub>max</sub>     | 9, 15, 16    | Maximum pin voltage (Ipin ≤1mA)          | Self-limited |      |

| I <sub>ZCD</sub>     | 11           | Zero current detector max. current       | ±5           | mA   |

| V <sub>MODE/SC</sub> | 12           | Voltage range                            | -0.3 to 5    | V    |

| V <sub>OSC</sub>     | 13           | Voltage range                            | -0.3 to 3.3  | V    |

| P <sub>TOT</sub>     |              | Power dissipation @T <sub>A</sub> = 50°C | 0.75         | W    |

### 3.2 Thermal data

Table 4. Thermal data

| Symbol            | Parameter                              | Value      | Unit |

|-------------------|----------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient | 120        | °C/W |

| T <sub>J</sub>    | Junction operating temperature range   | -40 to 150 | °C   |

Electrical characteristics L6566B

## 4 Electrical characteristics

(T<sub>J</sub> = -25 to 125°C, V<sub>CC</sub> = 12, C<sub>O</sub> = 1 nF; MODE/SC=V<sub>REF</sub>, R<sub>T</sub> = 20 k $\Omega$  from OSC to GND, unless otherwise specified).

**Table 5. Electrical characteristics**

| Symbol                 | Parameter                     | Test condition                                              | Min. | Тур. | Max. | Unit |

|------------------------|-------------------------------|-------------------------------------------------------------|------|------|------|------|

| Supply voltage         |                               |                                                             |      |      |      |      |

|                        | 0                             | V <sub>COMP</sub> > V <sub>COMPL</sub>                      | 10.6 |      | 23   | .,,  |

| Vcc                    | Operating range after turn-on | $V_{COMP} = V_{COMPO}$                                      | 8    |      | 23   | V    |

| Vcc <sub>On</sub>      | Turn-on threshold             | (1)                                                         | 13   | 14   | 15   | V    |

| Vac                    | Tive off three hold           | (1) V <sub>COMP</sub> > V <sub>COMPL</sub>                  | 9.4  | 10   | 10.6 | V    |

| Vcc <sub>Off</sub>     | Turn-off threshold            | $^{(1)}$ $V_{COMP} = V_{COMPO}$                             | 7.2  | 7.6  | 8.0  | V    |

| Hys                    | Hysteresis                    | V <sub>COMP</sub> > V <sub>COMPL</sub>                      |      | 4    |      | ٧    |

| V <sub>Z</sub>         | Zener voltage                 | Icc = 20 mA, IC disabled                                    | 23   | 25   | 27   | ٧    |

| Supply curi            | rent                          |                                                             |      |      |      |      |

| I <sub>start-up</sub>  | Start-up current              | Before turn-on, Vcc = 13 V                                  |      | 200  | 250  | μΑ   |

| Iq                     | Quiescent current             | After turn-on, V <sub>ZCD</sub> = V <sub>CS</sub> = 1V      |      | 2.6  | 2.8  | mA   |

| Icc                    | Operating supply current      | MODE/SC open                                                |      | 4    | 4.6  | mA   |

| 1                      | Quiescent current             | IC disabled <sup>(2)</sup>                                  | 330  |      | 2500 |      |

| I <sub>qdis</sub>      |                               | IC latched off                                              |      | 440  | 500  | μA   |

| High-voltag            | e start-up generator          |                                                             |      |      |      |      |

| V <sub>HV</sub>        | Breakdown voltage             | I <sub>HV</sub> < 100 μA                                    | 700  |      |      | V    |

| V <sub>HVstart</sub>   | Start voltage                 | I <sub>Vcc</sub> < 100 μA                                   | 65   | 80   | 100  | V    |

| I <sub>charge</sub>    | Vcc charge current            | V <sub>HV</sub> > V <sub>Hvstart</sub> , Vcc > 3V           | 0.55 | 0.85 | 1    | mA   |

| 1                      | ON-state current              | V <sub>HV</sub> > V <sub>Hvstart</sub> , Vcc > 3V           |      |      | 1.6  | m A  |

| I <sub>HV, ON</sub>    | ON-state current              | V <sub>HV</sub> > V <sub>Hvstart</sub> , Vcc = 0            |      |      | 0.8  | - mA |

| I <sub>HV, OFF</sub>   | OFF-state leakage current     | V <sub>HV</sub> = 400 V                                     |      |      | 40   | μΑ   |

|                        |                               | Vcc falling                                                 | 4.4  | 5    | 5.6  |      |

| V <sub>CCrestart</sub> | Vcc restart voltage           | (1) IC latched off                                          | 12.5 | 13.5 | 14.5 | J    |

| • Corestart            | 100 rootalit voltago          | (1) Disabled by<br>V <sub>COMP</sub> < V <sub>COMPOFF</sub> | 9.4  | 10   | 10.6 | •    |

Table 5. Electrical characteristics (continued)

| Symbol                | Parameter                | Test condition                                                     | Min.  | Тур.   | Max.  | Unit |

|-----------------------|--------------------------|--------------------------------------------------------------------|-------|--------|-------|------|

| Reference v           | roltage                  |                                                                    |       |        |       |      |

| V <sub>REF</sub>      | Output voltage           | $^{(1)}$ T <sub>J</sub> = 25 °C; I <sub>REF</sub> = 1 mA           | 4.95  | 5      | 5.05  | V    |

| V <sub>REF</sub>      | Total variation          | I <sub>REF</sub> = 1 to 5 mA,<br>Vcc= 10.6 to 23 V                 | 4.9   |        | 5.1   | ٧    |

| I <sub>REF</sub>      | Short circuit current    | V <sub>REF</sub> = 0                                               | 10    |        | 30    | mA   |

|                       | Sink capability in UVLO  | Vcc = 6V; Isink = 0.5 mA                                           |       | 0.2    | 0.5   | V    |

| V <sub>OV</sub>       | Overvoltage threshold    |                                                                    | 5.3   | 5.7    |       | ٧    |

| Internal osc          | illator                  |                                                                    |       |        |       |      |

|                       |                          | Operating range                                                    | 10    |        | 300   |      |

| f <sub>sw</sub>       | Oscillation frequency    | $T_J = 25$ °C, $V_{ZCD} = 0$ ,<br>MODE/SC = Open                   | 95    | 100    | 105   | kHz  |

|                       |                          | Vcc=12 to 23 V, V <sub>ZCD</sub> = 0,<br>MODE/SC = Open            | 93    | 100    | 107   |      |

| V <sub>OSC</sub>      | Voltage reference        | (3)                                                                | 0.97  | 1      | 1.03  | V    |

| D <sub>max</sub>      | Maximum duty cycle       | MODE/SC = Open,<br>V <sub>COMP</sub> = 5 V                         | 70    |        | 75    | %    |

| Brownout p            | rotection                |                                                                    |       |        |       |      |

| Vth                   | Throohold valtage        | Voltage falling (turn-off)                                         | 0.432 | 0.450  | 0.468 | ٧    |

| VIII                  | Threshold voltage        | Voltage rising (turn-on)                                           | 0.452 | 0.485  | 0.518 | V    |

| I <sub>Hys</sub>      | Current hysteresis       | Vcc > 5V, V <sub>VFF</sub> = 0.3V                                  | 12    | 15     | 18    | μA   |

| V <sub>AC_OK_CL</sub> | Clamp level              | $^{(1)}I_{AC_{-}OK} = 100\mu A$                                    | 3     | 3.15   | 3.3   | V    |

| Line voltage          | e feedforward            |                                                                    |       | I      | I.    |      |

|                       |                          | V <sub>VFF</sub> = 0 to 3 V, V <sub>ZCD</sub> < V <sub>ZCDth</sub> |       |        | -1    | μΑ   |

| $I_{VFF}$             | Input bias current       | V <sub>ZCD</sub> > V <sub>ZCDth</sub>                              | -0.7  | -1     |       | mA   |

| V <sub>VFF</sub>      | Linear operation range   |                                                                    |       | 0 to 3 |       | V    |

| V <sub>OFF</sub>      | IC disable voltage       |                                                                    | 3     | 3.15   | 3.3   | V    |

| V <sub>VFFlatch</sub> | Latch-off/clamp level    | $V_{ZCD} > V_{ZCDth}$                                              |       | 6.4    |       | ٧    |

| Kc                    | Control voltage gain (3) | V <sub>VFF</sub> = 1 V, V <sub>COMP</sub> = 4 V                    |       | 0.4    |       | V/V  |

| K <sub>FF</sub>       | Feedforward gain (3)     | V <sub>VFF</sub> = 1 V, V <sub>COMP</sub> = 4 V                    |       | 0.04   |       | V/V  |

Electrical characteristics L6566B

Table 5. Electrical characteristics (continued)

| Symbol                   | Parameter                   | Test condition                          | Min. | Тур. | Max. | Unit |  |

|--------------------------|-----------------------------|-----------------------------------------|------|------|------|------|--|

| Current sense comparator |                             |                                         |      |      |      |      |  |

| I <sub>CS</sub>          | Input bias current          | V <sub>CS</sub> = 0                     |      |      | -1   | μΑ   |  |

| t <sub>LEB</sub>         | Leading edge blanking       |                                         | 150  | 250  | 300  | ns   |  |

| td <sub>(H-L)</sub>      | Delay to output             |                                         |      |      | 100  | ns   |  |

|                          |                             | $V_{COMP} = V_{COMPHI}, V_{VFF} = 0V$   | 0.92 | 1    | 1.08 |      |  |

| V <sub>CSx</sub>         | Overcurrent setpoint        | $V_{COMP} = V_{COMPHI}, V_{VFF} = 1.5V$ | 0.45 | 0.5  | 0.55 | ٧    |  |

|                          |                             | $V_{COMP} = V_{COMPHI}, V_{VFF} = 3.0V$ |      | 0    | 0.1  |      |  |

| V <sub>CSdis</sub>       | Hiccup-mode OCP level       | (1)                                     | 1.4  | 1.5  | 1.6  | ٧    |  |

| PWM contro               | ol                          | •                                       |      |      |      |      |  |

| V <sub>COMPHI</sub>      | Upper clamp voltage         | I <sub>COMP</sub> = 0                   |      | 5.7  |      | V    |  |

| V <sub>COMPLO</sub>      | Lower Clamp Voltage         | I <sub>SOURCE</sub> = -1mA              |      | 2.0  |      | ٧    |  |

| V <sub>COMPSH</sub>      | Linear dynamics upper limit | (1) V <sub>VFF</sub> = 0V               | 4.8  | 5    | 5.2  | V    |  |

| I <sub>COMP</sub>        | Max. source current         | V <sub>COMP</sub> = 3.3 V               | 320  | 400  | 480  | μΑ   |  |

| R <sub>COMP</sub>        | Dynamic resistance          | V <sub>COMP</sub> = 2.6 to 4.8 V        |      | 25   |      | kΩ   |  |

|                          |                             | (1)                                     | 2.52 | 2.65 | 2.78 | .,   |  |

| V <sub>COMPBM</sub>      | Burst-mode threshold        | (1) MODE/SC = Open                      | 2.7  | 2.85 | 3    | V    |  |

| Hys                      | Burst-mode hysteresis       |                                         |      | 20   |      | mV   |  |

| I <sub>CLAMPL</sub>      | Lower clamp capability      | V <sub>COMP</sub> = 2V                  | -3.5 |      | -1.5 | mA   |  |

| V <sub>COMPOFF</sub>     | Disable threshold           | Voltage falling                         |      | 1.4  |      | ٧    |  |

| V                        | Level for lower UVLO off    | (3)                                     | 2.61 | 2.75 | 2.89 | V    |  |

| V <sub>COMPO</sub>       | threshold (voltage falling) | (3) MODE/SC = Open                      | 3.02 | 3.15 | 3.28 | V    |  |

| V                        | Level for higher UVLO off   | (3)                                     | 2.9  | 3.05 | 3.2  | V    |  |

| V <sub>COMPL</sub>       | threshold (voltage rising)  | (3) MODE/SC = Open                      | 3.41 | 3.55 | 3.69 | V    |  |

Table 5. Electrical characteristics (continued)

| Symbol              | Parameter                             | Test condition                                                                            | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| Zero curren         | t detector/ overvoltage protec        | tion                                                                                      | •    | •    |      |      |

| V <sub>ZCDH</sub>   | Upper clamp voltage                   | I <sub>ZCD</sub> = 3 mA                                                                   | 5.4  | 5.7  | 6    | V    |

| V <sub>ZCDL</sub>   | Lower clamp voltage                   | I <sub>ZCD</sub> = - 3 mA                                                                 |      | -0.4 |      | V    |

| V <sub>ZCDA</sub>   | Arming voltage                        | (1) positive-going edge                                                                   | 85   | 100  | 115  | mV   |

| V <sub>ZCDT</sub>   | Triggering voltage                    | (1) negative-going edge                                                                   | 30   | 50   | 70   | mV   |

| I <sub>ZCD</sub>    | Internal pull-up                      | V <sub>COMP</sub> < V <sub>COMPSH</sub>                                                   |      |      | -1   | μА   |

|                     |                                       | VZCD < 2 V, V <sub>COMP</sub> = V <sub>COMPHI</sub>                                       | -130 | -100 | -70  |      |

| I <sub>ZCDsrc</sub> | Source current capability             | $V_{ZCD} = V_{ZCDL}$                                                                      | -3   |      |      | mA   |

| I <sub>ZCDsnk</sub> | Sink current capability               | $V_{ZCD} = V_{ZCDH}$                                                                      | 3    |      |      | mA   |

| T <sub>BLANK1</sub> | Turn-on inhibit time                  | After gate-drive going low                                                                |      | 2.5  |      | μs   |

| V <sub>ZCDth</sub>  | OVP threshold                         |                                                                                           | 4.85 | 5    | 5.15 | ٧    |

| T <sub>BLANK2</sub> | OVP strobe delay                      | After gate-drive going low                                                                |      | 2    |      | μs   |

| Latched sh          | utdown function                       | •                                                                                         |      |      | •    | •    |

| I <sub>OTP</sub>    | Input bias current                    | V <sub>DIS</sub> = 0 to V <sub>OTP</sub>                                                  |      |      | -1   | μA   |

| V <sub>OTP</sub>    | Disable threshold                     | (1)                                                                                       | 4.32 | 4.5  | 4.68 | V    |

| Thermal sh          | utdown                                | •                                                                                         |      |      | •    | •    |

| Vth                 | Shutdown threshold                    |                                                                                           |      | 160  |      | °C   |

| Hys                 | Hysteresis                            |                                                                                           |      | 50   |      | °C   |

| External os         | cillator (frequency modulation        | )                                                                                         |      |      |      |      |

| f <sub>FMOD</sub>   | Oscillation frequency                 | C <sub>MOD</sub> = 0.1 μF                                                                 | 600  | 750  | 900  | Hz   |

|                     | Usable frequency range                |                                                                                           | 0.05 |      | 15   | kHz  |

| V <sub>pk</sub>     | Peak voltage                          | (3)                                                                                       |      | 1.5  |      | V    |

| V <sub>vy</sub>     | Valley voltage                        |                                                                                           |      | 0.5  |      | ٧    |

| I <sub>FMOD</sub>   | Charge/discharge current              |                                                                                           |      | 150  |      | μA   |

| Mode selec          | tion / slope compensation             |                                                                                           |      |      |      |      |

| MODE <sub>th</sub>  | Threshold for QR operation            |                                                                                           |      | 3    |      | V    |

| SC <sub>pk</sub>    | Ramp peak<br>(MODE/SC = Open)         | $R_{S-COMP} = 3 \text{ k}\Omega \text{ to GND, GD pin}$<br>high, $V_{COMP} = 5 \text{ V}$ |      | 1.7  |      | V    |

| SC <sub>vy</sub>    | Ramp starting value (MODE/SC = Open)  | $R_{S-COMP} = 3 \text{ k}\Omega \text{ to GND},$<br>GD pin high                           |      | 0.3  |      | V    |

|                     | Ramp voltage<br>(MODE/SC = Open)      | GD pin low                                                                                |      | 0    |      | V    |

|                     | Source capability<br>(MODE/SC = Open) | $V_{S-COMP} = V_{S-COMPpk}$                                                               | 0.8  |      |      | mA   |

Electrical characteristics L6566B

Table 5. Electrical characteristics (continued)

| Symbol                | Parameter                  | Test condition                                                                                    | Min. | Тур. | Max. | Unit |  |  |  |  |

|-----------------------|----------------------------|---------------------------------------------------------------------------------------------------|------|------|------|------|--|--|--|--|

| Soft-start Soft-start |                            |                                                                                                   |      |      |      |      |  |  |  |  |

| I <sub>SS1</sub>      | - Charge current           | T <sub>J</sub> = 25 °C, V <sub>SS</sub> < 2 V,<br>V <sub>COMP</sub> = 4 V                         | 14   | 20   | 26   | - μΑ |  |  |  |  |

| I <sub>SS2</sub>      |                            | $T_J = 25  ^{\circ}\text{C},  V_{\text{SS}} > 2  \text{V},$ $V_{\text{COMP}} = V_{\text{COMPHi}}$ | 3.5  | 5    | 6.5  |      |  |  |  |  |

| I <sub>SSdis</sub>    | Discharge current          | V <sub>SS</sub> > 2 V                                                                             | 3.5  | 5    | 6.5  | μΑ   |  |  |  |  |

| V <sub>SSclamp</sub>  | High saturation voltage    | V <sub>COMP</sub> = 4 V                                                                           |      | 2    |      | V    |  |  |  |  |

| V <sub>SSDIS</sub>    | Disable level              | (1) V <sub>COMP</sub> =V <sub>COMPHi</sub>                                                        | 4.85 | 5    | 5.15 | V    |  |  |  |  |

| V <sub>SSLAT</sub>    | Latch-off level            | V <sub>COMP</sub> =V <sub>COMPHi</sub>                                                            |      | 6.4  |      | V    |  |  |  |  |

| Gate driver           |                            |                                                                                                   |      |      |      |      |  |  |  |  |

| V <sub>GDH</sub>      | Output high voltage        | I <sub>GDsource</sub> = 5 mA, Vcc = 12V                                                           | 9.8  | 11   |      | V    |  |  |  |  |

| $V_{GDL}$             | Output low voltage         | I <sub>GDsink</sub> = 100 mA                                                                      |      | 0.75 |      | V    |  |  |  |  |

| I <sub>sourcepk</sub> | Output source peak current |                                                                                                   | -0.6 |      |      | Α    |  |  |  |  |

| I <sub>sinkpk</sub>   | Output sink peak current   |                                                                                                   | 0.8  |      |      | Α    |  |  |  |  |

| t <sub>f</sub>        | Fall time                  |                                                                                                   |      | 40   |      | ns   |  |  |  |  |

| t <sub>r</sub>        | Rise time                  |                                                                                                   |      | 50   |      | ns   |  |  |  |  |

| V <sub>GDclamp</sub>  | Output clamp voltage       | I <sub>GDsource</sub> = 5mA; Vcc = 20V                                                            | 10   | 11.3 | 15   | V    |  |  |  |  |

|                       | UVLO saturation            | Vcc = 0 to Vccon, Isink = 1mA                                                                     |      | 0.9  | 1.1  | V    |  |  |  |  |

<sup>1.</sup> Parameters tracking one another.

<sup>2.</sup> See Table 6 on page 41 and Table 7 on page 42

<sup>3.</sup> The Voltage Feedforward block output is given by:  $V_{cs} = Kc (V_{COMP} - 2.5) - K_{FF} V_{VFF}$

## 5 Application information

The L6566B is a versatile peak-current-mode PWM controller specific for offline flyback converters. The device allows either Fixed-Frequency (FF) or Quasi-Resonant (QR) operation, selectable with the pin MODE/SC (12): forcing the voltage on the pin over 3V (e.g. by tying it to the 5V reference externally available at pin VREF, 10) will activate QR operation, otherwise the device will be FF-operated.

Irrespective of the operating option selected by pin 12, the device is able to work in different modes, depending on the converter's load conditions. If QR operation is selected (see *Figure 4*):

- 1. QR mode at heavy load. Quasi-resonant operation lies in synchronizing MOSFET's turn-on to the transformer's demagnetization by detecting the resulting negative-going edge of the voltage across any winding of the transformer. Then the system works close to the boundary between discontinuous (DCM) and continuous conduction (CCM) of the transformer. As a result, the switching frequency will be different for different line/load conditions (see the hyperbolic-like portion of the curves in Figure 4). Minimum turn-on losses, low EMI emission and safe behavior in short circuit are the main benefits of this kind of operation.

- 2. Valley-skipping mode at medium/ light load. The externally programmable oscillator of the L6566B, synchronized to MOSFET's turn-on, enables the designer to define the maximum operating frequency of the converter. As the load is reduced MOSFET's turnon will not any more occur on the first valley but on the second one, the third one and so on. In this way the switching frequency will no longer increase (piecewise linear portion in *Figure 4*).

- 3. Burst-mode with no or very light load. When the load is extremely light or disconnected, the converter will enter a controlled on/off operation with constant peak current. Decreasing the load will then result in frequency reduction, which can go down even to few hundred hertz, thus minimizing all frequency-related losses and making it easier to comply with energy saving regulations or recommendations. Being the peak current very low, no issue of audible noise arises.

Figure 4. Multi-mode operation with QR option active

If FF operation is selected:

1. FF mode from heavy to light load. The system operates exactly like a standard current mode control, at a frequency f<sub>sw</sub> determined by the externally programmable oscillator: both DCM and CCM transformer operation are possible, depending on whether the power that it processes is greater or less than:

#### **Equation 1**

$$Pin_{T} = \frac{\left(\frac{Vin V_{R}}{Vin + V_{R}}\right)^{2}}{2 f_{sw} Lp}$$

where Vin is the input voltage to the converter,  $V_R$  the reflected voltage (i.e. the regulated output voltage times the primary-to-secondary turn ratio) and Lp the inductance of the primary winding. Pin<sub>T</sub> is the power level that marks the transition from continuous to discontinuous operation mode of the transformer.

2. Burst-mode with no or very light load. This kind of operation is activated in the same way and results in the same behavior as previously described for QR operation.

The L6566B is specifically designed for applications with no PFC front-end; pin 6 (FMOD) features an auxiliary oscillator that can modulate the switching frequency (when FF operation is selected) in order to mitigate EMI emissions by a spread-spectrum action.

### 5.1 High-voltage start-up generator

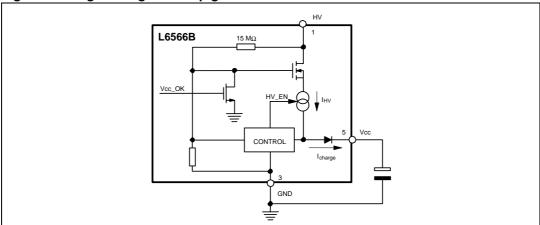

Figure 5 shows the internal schematic of the high-voltage start-up generator (HV generator). It is made up of a high-voltage N-channel FET, whose gate is biased by a 15 M $\Omega$  resistor, with a temperature-compensated current generator connected to its source.

Figure 5. High-voltage start-up generator: internal schematic

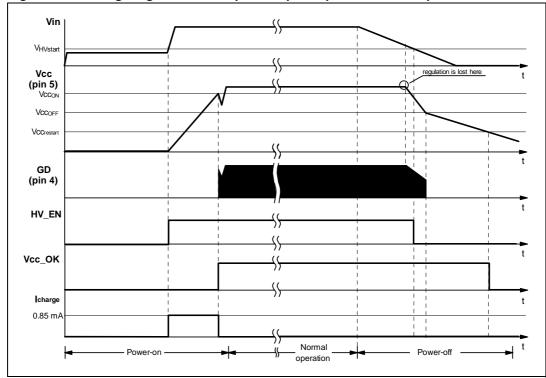

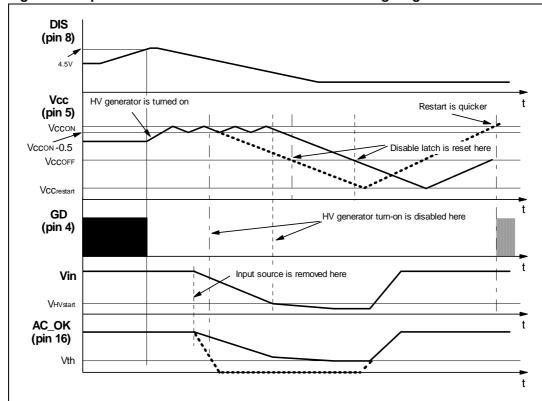

With reference to the timing diagram of *Figure 6*, when power is first applied to the converter the voltage on the bulk capacitor (Vin) builds up and, at about 80V, the HV generator is enabled to operate (HV\_EN is pulled high) so that it draws about 1 mA. This current, minus the device's consumption, charges the bypass capacitor connected from pin Vcc (5) to ground and makes its voltage rise almost linearly.

Figure 6. Timing diagram: normal power-up and power-down sequences

As the Vcc voltage reaches the turn-on threshold (14V typ.) the device starts operating and the HV generator is cut off by the Vcc\_OK signal asserted high. The device is powered by the energy stored in the Vcc capacitor until the self-supply circuit (typically an auxiliary winding of the transformer and a steering diode) develops a voltage high enough to sustain the operation. The residual consumption of this circuit is just the one on the 15 M $\Omega$  resistor ( $\approx$  10 mW at 400 Vdc), typically 50-70 times lower, under the same conditions, as compared to a standard start-up circuit made with external dropping resistors.

At converter power-down the system will lose regulation as soon as the input voltage is so low that either peak current or maximum duty cycle limitation is tripped. Vcc will then drop and stop IC activity as it falls below the UVLO threshold (10V typ.). The Vcc\_OK signal is de-asserted as the Vcc voltage goes below a threshold VCC<sub>rest</sub> located at about 5V. The HV generator can now restart. However, if Vin < Vin<sub>start</sub>, as illustrated in *Figure 6*, HV\_EN is de-asserted too and the HV generator is disabled. This prevents converter's restart attempts and ensures monotonic output voltage decay at power-down in systems where brownout protection (see the relevant section) is not used.

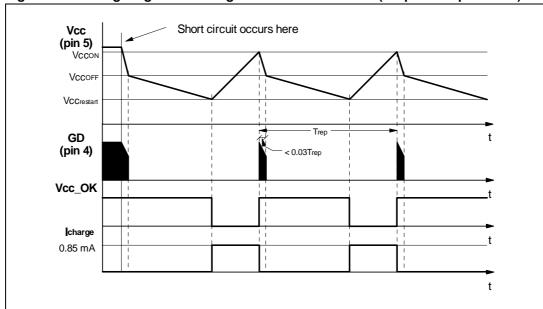

The low restart threshold VCC<sub>rest</sub> ensures that, during short circuits, the restart attempts of the device will have a very low repetition rate, as shown in the timing diagram of *Figure 7 on page 20*, and that the converter will work safely with extremely low power throughput.

Figure 7. Timing diagram showing short-circuit behavior (SS pin clamped at 5V)

Figure 8. Zero current detection block, triggering block, oscillator block and related logic

### 5.2 Zero current detection and triggering block; oscillator block

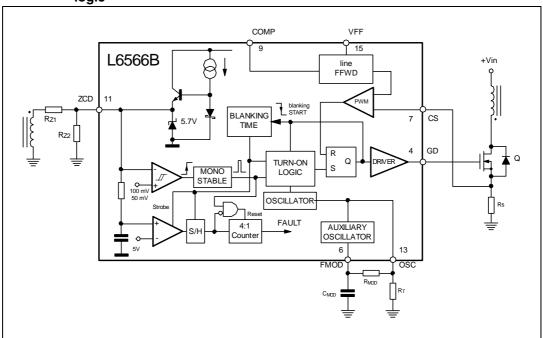

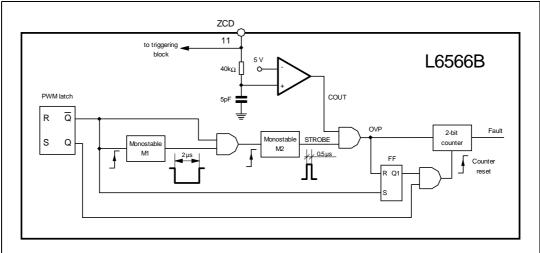

The Zero Current Detection (ZCD) and Triggering blocks switch on the external MOSFET if a negative-going edge falling below 50 mV is applied to the input (pin 11, ZCD). To do so the triggering block must be previously armed by a positive-going edge exceeding 100 mV.

This feature is typically used to detect transformer demagnetization for QR operation, where the signal for the ZCD input is obtained from the transformer's auxiliary winding used also to supply the L6566B. The triggering block is blanked for  $T_{BLANK} = 2.5 \,\mu s$  after MOSFET's turn-off to prevent any negative-going edge that follows leakage inductance demagnetization from triggering the ZCD circuit erroneously.

The voltage at the pin is both top and bottom limited by a double clamp, as illustrated in the internal diagram of the ZCD block of *Figure 8 on page 20*. The upper clamp is typically located at 5.7 V, while the lower clamp is located at -0.4V. The interface between the pin and the auxiliary winding will be a resistor divider. Its resistance ratio will be properly chosen (see *Section 5.11: OVP block on page 35*) and the individual resistance values ( $R_{Z1}$ ,  $R_{Z2}$ ) will be such that the current sourced and sunk by the pin be within the rated capability of the internal clamps ( $\pm 3$  mA).

At converter power-up, when no signal is coming from the ZCD pin, the oscillator starts up the system. The oscillator is programmed externally by means of a resistor ( $R_T$ ) connected from pin OSC (13) to ground. With good approximation the oscillation frequency  $f_{osc}$  will be:

### **Equation 2**

$$f_{osc} \approx \frac{2 \cdot 10^3}{R_T}$$

(with  $f_{\rm osc}$  in kHz and  $R_{\rm T}$  in  $k\Omega$ ). As the device is turned on, the oscillator starts immediately; at the end of the first oscillator cycle, being zero the voltage on the ZCD pin, the MOSFET will be turned on, thus starting the first switching cycle right at the beginning of the second oscillator cycle. At any switching cycle, the MOSFET is turned off as the voltage on the current sense pin (CS, 7) hits an internal reference set by the Line Feedforward block, and the transformer starts demagnetization. If this completes (hence a negative-going edge appears on the ZCD pin) after a time exceeding one oscillation period  $T_{\rm osc}=1/f_{\rm osc}$  from the previous turn-on, the MOSFET will be turned on again - with some delay to ensure minimum voltage at turn-on – and the oscillator ramp will be reset. If, instead, the negative-going edge appears before  $T_{\rm osc}$  has elapsed, it will be ignored and only the first negative-going edge after  $T_{\rm osc}$  will turn-on the MOSFET and synchronize the oscillator. In this way one or more drain ringing cycles will be skipped ("valley-skipping mode", *Figure 9*) and the switching frequency will be prevented from exceeding  $f_{\rm osc}$ .

5/

Figure 9. Drain ringing cycle skipping as the load is gradually reduced

Note:

When the system operates in valley skipping-mode, uneven switching cycles may be observed under some line/load conditions, due to the fact that the OFF-time of the MOSFET is allowed to change with discrete steps of one ringing cycle, while the OFF-time needed for cycle-by-cycle energy balance may fall in between. Thus one or more longer switching cycles will be compensated by one or more shorter cycles and vice versa. However, this mechanism is absolutely normal and there is no appreciable effect on the performance of the converter or on its output voltage.

If the MOSFET is enabled to turn on but the amplitude of the signal on the ZCD pin is smaller than the arming threshold for some reason (e.g. a heavy damping of drain oscillations, like in some single-stage PFC topologies, or when a turn-off snubber is used), MOSFET's turn-on cannot be triggered. This case is identical to what happens at start-up: at the end of the next oscillator cycle the MOSFET will be turned on, and a new switching cycle will take place after skipping no more than one oscillator cycle.

The operation described so far does not consider the blanking time  $T_{BLANK}$  after MOSFET's turn off, and actually  $T_{BLANK}$  does not come into play as long as the following condition is met:

#### **Equation 3**

$$D \le 1 - \frac{T_{BLANK}}{T_{osc}}$$

where D is the MOSFET duty cycle. If this condition is not met, things do not change substantially: the time during which MOSFET's turn-on is inhibited is extended beyond  $T_{\rm osc}$  by a fraction of  $T_{\rm BLANK}$ . As a consequence, the maximum switching frequency will be a little lower than the programmed value  $f_{\rm osc}$  and valley-skipping mode may take place slightly earlier than expected. However this is quite unusual: setting  $f_{\rm osc}$  = 150 kHz, the phenomenon can be observed at duty cycles higher than 60%. See *Section 5.11: OVP block on page 35* for further implications of  $T_{\rm BLANK}$ .

If the voltage on the COMP pin (9) saturates high, which reveals an open control loop, an internal pull-up keeps the ZCD pin close to 2V during MOSFET's OFF-time to prevent noise from false triggering the detection block. When this pull-up is active, the ZCD pin might not be able to go below the triggering threshold, which would stop the converter. To allow autorestart operation, however ensuring minimum operating frequency in these conditions, the oscillator frequency that retriggers MOSFET's turn-on is that of the external oscillator divided by 128. Additionally, to prevent malfunction at converter's start-up, the pull-up is disabled during the initial soft-start (see the relevant section). However, to ensure a correct

start-up, at the end of the soft-start phase the output voltage of the converter must meet the condition:

#### **Equation 4**

$$Vout > \frac{Ns}{Naux} R_{Z1} I_{ZCD}$$

where Ns is the turn number of the secondary winding, Naux the turn number of the auxiliary winding and  $I_{ZCD}$  the maximum pull-up current (130  $\mu$ A).

The operation described so far under different operating conditions for the converter is illustrated in the timing diagrams of *Figure 10*.

If the FF option is selected the operation will be exactly equal to that of a standard current-mode PWM controller. It will work at a frequency fsw = fosc; both DCM and CCM transformer's operation are possible, depending on the operating conditions (input voltage and output load) and on the design of the power stage. The MOSFET is turned on at the beginning of each oscillator cycle and is turned off as the voltage on the current sense pin reaches an internal reference set by the Line Feedforward block. The maximum duty cycle is limited at 70% minimum. The signal on the ZCD pin in this case is used only for detecting feedback loop failures (see Section 5.11: OVP block on page 35).

ZCD ZCD ZCD (pin 11) (pin 11) 50 m) Oscillato Oscillator Oscillator ramp ramp ramp ZCD ZCD ZCD blanking blanking blanking time time time Arm/Trigge Arm/Trigger Arm/Trigge ON-enable ON-enable PWM latch PWM latch PWM latch Set

b) light load

PWM latch

Reset

GD

(pin 4)

c) start-up

Figure 10. Operation of ZCD, triggering and oscillator blocks (QR option active)

PWM latch

Reset

GD

(pin 4)

4

PWM latch

Reset

GD

(pin 4)

a) full load

### 5.3 Burst-mode operation at no load or very light load

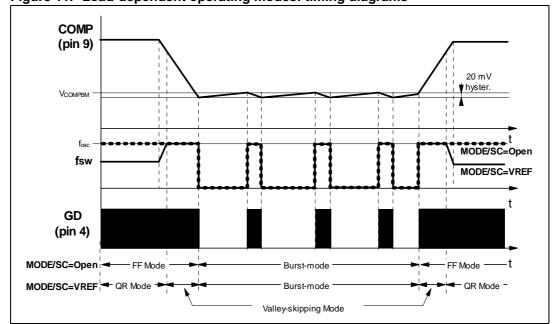

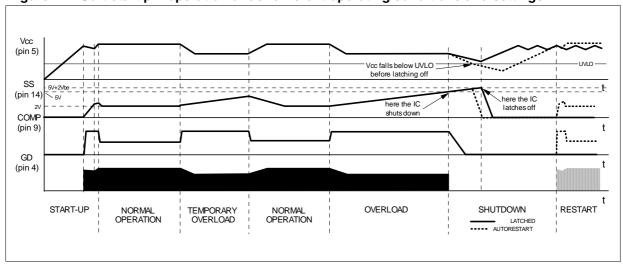

When the voltage at the COMP pin (9) falls 20 mV below a threshold fixed internally at a value,  $V_{COMPBM}$ , depending on the selected operating mode, the L6566B is disabled with the MOSFET kept in OFF state and its consumption reduced at a lower value to minimize Vcc capacitor discharge.

The control voltage now will increase as a result of the feedback reaction to the energy delivery stop (the output voltage will be slowly decaying), the threshold will be exceeded and the device will restart switching again. In this way the converter will work in burst-mode with a nearly constant peak current defined by the internal disable level. A load decrease will then cause a frequency reduction, which can go down even to few hundred hertz, thus minimizing all frequency-related losses and making it easier to comply with energy saving regulations. This kind of operation, shown in the timing diagrams of *Figure 11* along with the others previously described, is noise-free since the peak current is low.

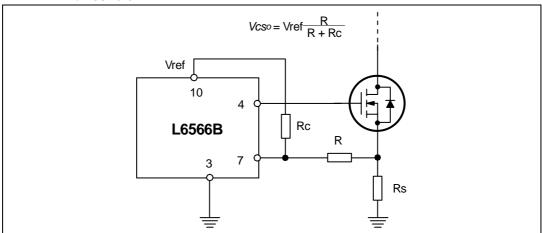

If it is necessary to decrease the intervention threshold of the burst-mode operation, this can be done by adding a small DC offset on the current sense pin as shown in *Figure 12 on page 25*.

Note: The offset reduces the available dynamics of the current signal; thereby, the value of the sense resistor must be determined taking this offset into account.

Figure 11. Load-dependent operating modes: timing diagrams

Figure 12. Addition of an offset to the current sense lowers the burst-mode operation threshold

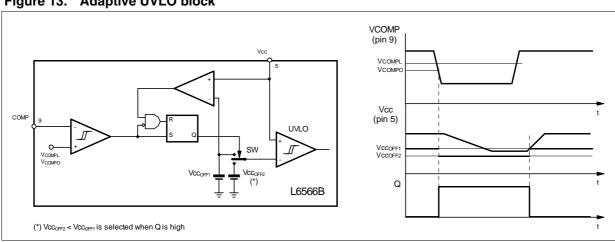

#### 5.4 **Adaptive UVLO**

A major problem when optimizing a converter for minimum no-load consumption is that the voltage generated by the auxiliary winding under these conditions falls considerably as compared even to a few mA load. This very often causes the supply voltage Vcc of the control IC to drop and go below the UVLO threshold so that the operation becomes intermittent, which is undesired. Furthermore, this must be traded off against the need of generating a voltage not exceeding the maximum allowed by the control IC at full load.

To help the designer overcome this problem, the device, besides reducing its own consumption during burst-mode operation, also features a proprietary adaptive UVLO function. It consists of shifting the UVLO threshold downwards at light load, namely when the voltage at pin COMP falls below a threshold  $V_{COMPO}$  internally fixed, so as to have more headroom. To prevent any malfunction during transients from minimum to maximum load the normal (higher) UVLO threshold is re-established when the voltage at pin COMP exceeds  $V_{\text{COMPL}}$  and  $V_{$ normal UVLO threshold ensures that at full load the MOSFET will be driven with a proper gate-to-source voltage.

Figure 13. Adaptive UVLO block

### 5.5 PWM control block

The device is specific for secondary feedback. Typically, there is a TL431 on the secondary side and an optocoupler that transfers output voltage information to the PWM control on the primary side, crossing the isolation barrier. The PWM control input (pin 9, COMP) is driven directly by the phototransistor's collector (the emitter is grounded to GND) to modulate the duty cycle (*Figure 14*, left-hand side circuit).

In applications where a tight output regulation is not required, it is possible to use a primary-sensing feedback technique. In this approach the voltage generated by the self-supply winding is sensed and regulated. This solution, shown in *Figure 14*, right-hand side circuit, is cheaper because no optocoupler or secondary reference is needed, but output voltage regulation, especially as a result of load changes, is quite poor.

L6566B

COMP

COMP

Secondary feedback

Primary feedback

Figure 14. Possible feedback configurations that can be used with the L6566B

Ideally, the voltage generated by the self-supply winding and the output voltage should be related by the Naux/Ns turn ratio only. Actually, numerous non-idealities, mainly transformer's parasitics, cause the actual ratio to deviate from the ideal one. Line regulation is quite good, in the range of  $\pm$  2%, whereas load regulation is about  $\pm$ 5% and output voltage tolerance is in the range of  $\pm$ 10%.

The dynamics of the pin is in the 2.5 to 5V range. The voltage at the pin is clamped downwards at about 2 V. If the clamp is externally overridden and the voltage on the pin is pulled below 1.4V the L6566B will shut down. This condition is latched as long as the device is supplied. While the device is disabled, however, no energy is coming from the self-supply circuit, thus the voltage on the Vcc capacitor will decay and cross the UVLO threshold after some time, which clears the latch and lets the HV generator restart. This function is intended for an externally controlled burst-mode operation at light load with a reduced output voltage, a technique typically used in multi-output SMPS, such as those for TVs or monitors (see the timing diagram *Figure 15 on page 27*).

Figure 15. Externally controlled burst-mode operation by driving pin COMP: timing diagram

### 5.6 PWM comparator, PWM latch and voltage feedforward blocks

The PWM comparator senses the voltage across the current sense resistor Rs and, by comparing it to the programming signal delivered by the feedforward block, determines the exact time when the external MOSFET is to be switched off. Its output resets the PWM latch, previously set by the oscillator or the ZCD triggering block, which will assert the gate driver output low. The use of PWM latch avoids spurious switching of the MOSFET that might result from the noise generated ("double-pulse suppression").

Cycle-by-cycle current limitation is realized with a second comparator (OCP comparator) that senses the voltage across the current sense resistor Rs as well and compares this voltage to a reference value V<sub>csx</sub>. Its output is or-ed with that of the PWM comparator (see the circuit schematic in *Figure 17 on page 29*). In this way, if the programming signal delivered by the feedforward block and sent to the PWM comparator exceeds V<sub>csx</sub>, it will be the OCP comparator to reset first the PWM latch instead of the PWM comparator. The value of V<sub>csx</sub>, thereby, determines the overcurrent setpoint along with the sense resistor Rs.

The power that QR flyback converters with a fixed overcurrent setpoint (like fixed-frequency systems) are able to deliver changes with the input voltage considerably. With wide-range mains, at maximum line it can be more than twice the value at minimum line, as shown by the upper curve in the diagram of *Figure 16 on page 28*. The device has the Line Feedforward function available to solve this issue.

It acts on the overcurrent setpoint V<sub>csx</sub>, so that it is a function of the converter's input voltage Vin sensed through a dedicated pin (15, VFF): the higher the input voltage, the lower the

setpoint. This is illustrated in the diagram on the left-hand side of *Figure 17 on page 29*: it shows the relationship between the voltage on the pin VFF and  $V_{CSX}$  (with the error amplifier saturated high in the attempt of keeping output voltage regulation):

#### **Equation 5**

$$V_{csx} = 1 - \frac{V_{VFF}}{3} = 1 - \frac{k}{3} Vin$$

Figure 16. Typical power capability change vs. input voltage in QR flyback converters

Note:

If the voltage on the pin exceeds 3V switching ceases but the soft-start capacitor is not discharged. The schematic in Figure 17 on page 29 shows also how the function is included in the control loop.

With a proper selection of the external divider R1-R2, i.e. of the ratio k = R2 / (R1+R2), it is possible to achieve the optimum compensation described by the lower curve in the diagram of *Figure 16*.

The optimum value of k,  $k_{opt}$ , which minimizes the power capability variation over the input voltage range, is the one that provides equal power capability at the extremes of the range. The exact calculation is complex, and non-idealities shift the real-world optimum value from the theoretical one. It is therefore more practical to provide a first cut value, simple to be calculated, and then to fine tune experimentally.

Assuming that the system operates exactly at the boundary between DCM and CCM, and neglecting propagation delays, the following expression for  $k_{opt}$  can be found:

#### **Equation 6**

$$k_{opt} = 3 \cdot \frac{V_R}{V_{inmin} \cdot V_{inmax} + (V_{inmin} + V_{inmax}) \cdot V_R}$$

Experience shows that this value is typically lower than the real one. Once the maximum peak primary current,  $I_{PKpmax}$ , occurring at minimum input voltage Vinmin has been found, the value of Rs can be determined from (5):

#### **Equation 7**

$$Rs = \frac{1 - \frac{k_{opt}}{3} V_{inmin}}{I_{PKpmax}}$$

Figure 17. Left: Overcurrent setpoint vs. VFF voltage; right: Line Feedforward function block

The converter is then tested on the bench to find the output power level  $Pout_{lim}$  where regulation is lost (because overcurrent is being tripped) both at  $Vin = Vin_{min}$  and  $Vin = Vin_{max}$ .

If  $Pout_{lim} @ Vin_{max} > Pout_{lim} @ Vin_{min}$  the system is still undercompensated and k needs increasing; if  $Pout_{lim} @ Vin_{max} < Pout_{lim} @ Vin_{min}$  the system is overcompensated and k needs decreasing. This will go on until the difference between the two values is acceptably low. Once found the true  $k_{opt}$  in this way, it is possible that  $Pout_{lim}$  turns out slightly different from the target; to correct this, the sense resistor Rs needs adjusting and the above tuning process will be repeated with the new Rs value. Typically a satisfactory setting is achieved in no more than a couple of iterations.

In applications where this function is not wanted, e.g. because of a narrow input voltage range, the VFF pin can be simply grounded, directly or through a resistor (see "Section 5.11: OVP block on page 35"). The overcurrent setpoint will be then fixed at the maximum value of 1V. If a lower setpoint is desired to reduce the power dissipation on Rs, the pin can be also biased at a fixed voltage using a divider from VREF (pin 10).

If the FF option is selected the Line Feedforward function can be still used to compensate for the total propagation delay Td of the current sense chain (internal propagation delay  $td_{(H-L)}$  plus the turn-off delay of the external MOSFET), which in standard current mode PWM controllers is done by adding an offset on the current sense pin proportional to the input voltage. In that case the divider ratio k, which will be much smaller as compared to that used with the QR option selected, can be calculated with the following equation:

#### **Equation 8**

$$k_{opt} = 3 \frac{Td}{RsLp}$$

where Lp is the inductance of the primary winding. In case a constant maximum power capability vs. the input voltage is not required, the VFF pin can be grounded, directly or through a resistor (see *Section 5.11: OVP block on page 35*), hence fixing the overcurrent setpoint at 1V, or biased at a fixed voltage through a divider from VREF to get a lower setpoint.

It is possible to bypass the pin to ground with a small film capacitor (e.g. 1-10 nF) to ensure a clean operation of the IC even in a noisy environment.

The pin is internally forced to ground during UVLO, after activating any latched protection and when pin COMP is pulled below its low clamp voltage (see *Section 5.5: PWM control block on page 26*).

### 5.7 Hiccup-mode OCP

A third comparator senses the voltage on the current sense input and shuts down the device if the voltage on the pin exceeds 1.5 V, a level well above that of the maximum overcurrent setpoint (1V). Such an anomalous condition is typically generated by either a short circuit of the secondary rectifier or a shorted secondary winding or a hard-saturated flyback transformer.

Figure 18. Hiccup-mode OCP: timing diagram

To distinguish an actual malfunction from a disturbance (e.g. induced during ESD tests), the first time the comparator is tripped the protection circuit enters a "warning state". If in the next switching cycle the comparator is not tripped, a temporary disturbance is assumed and the protection logic will be reset in its idle state; if the comparator will be tripped again a real malfunction is assumed and the L6566B will be stopped. Depending on the time relationship

between the detected event and the oscillator, occasionally the device could stop after the third detection.

This condition is latched as long as the device is supplied. While it is disabled, however, no energy is coming from the self-supply circuit; hence the voltage on the Vcc capacitor will decay and cross the UVLO threshold after some time, which clears the latch. The internal start-up generator is still off, then the Vcc voltage still needs to go below its restart voltage before the Vcc capacitor is charged again and the device restarted. Ultimately, this will result in a low-frequency intermittent operation (Hiccup-mode operation), with very low stress on the power circuit. This special condition is illustrated in the timing diagram of *Figure 18 on page 30*.

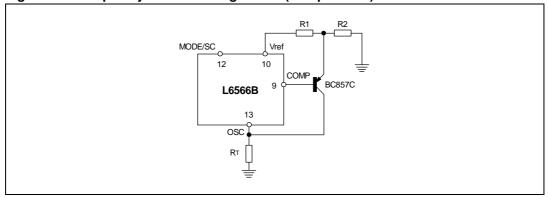

### 5.8 Frequency modulation

To alleviate converter's EMI emissions and reduce cost and size of the line filter, it is advantageous to modulate its switching frequency, so that the resulting spread-spectrum action distributes the energy of each harmonic of the switching frequency over a number of side-band harmonics. Their overall energy will be unchanged but the individual amplitudes will be smaller. This is what naturally occurs with QR operation, due to the twice-mains-frequency ripple appearing on the input bulk capacitor, which translates into different DCM-CCM boundary frequencies.

The L6566B is provided with a dedicated pin, FMOD (6), to perform this function if FF mode is selected.

Figure 19. Frequency modulation circuit