www.ti.com

# Fully Integrated Switch-Mode One-Cell Li-lon Charger with Full USB Compliance and **USB-OTG Support**

#### **FEATURES**

- **Charge Faster than Linear Chargers**

- **High-Accuracy Voltage and Current Regulation**

- Input Current Regulation Accuracy: ±5% (100 mA and 500 mA)

- Charge Voltage Regulation Accuracy: ±0.5% (25°C), ±1% (0°C-125°C)

- Charge Current Regulation Accuracy: ±5%

- High-Efficiency Mini-USB/AC Battery Charger for Single-Cell Li-Ion and Li-Polymer Battery **Packs**

- 20-V Absolute Maximum Input Voltage Rating

- 6-V Maximum Operating Input Voltage

- **Built-In Input Current Sensing and Limiting**

- Integrated Power FETs for Up To 1.25-A **Charge Rate**

- **Programmable Charge Parameters through** I<sup>2</sup>C<sup>™</sup> Interface (up to 3.4 Mbps):

- Input Current

- **Fast-Charge/Termination Current**

- Charge Voltage (3.5 V to 4.44 V)

- **Safety Timer**

- Termination Enable

- Synchronous Fixed-Frequency PWM Controller Operating at 3 MHz with 0% to 99.5% Duty Cycle

- **Automatic High Impedance Mode for Low Power Consumption**

- **Safety Timer with Reset Control**

- **Reverse Leakage Protection Prevents Battery** Drainage

- **Thermal Regulation and Protection**

- Input/Output Overvoltage Protection

- **Status Output for Charging and Faults**

- **USB Friendly Boot-Up Sequence**

- **Automatic Charging**

- **Power up System without Battery**

- **Boost Mode Operation for USB OTG:**

- Input Voltage Range (from Battery): 2.5 V to 4.5 V

- **Output Voltage for VBUS: 5.05 V**

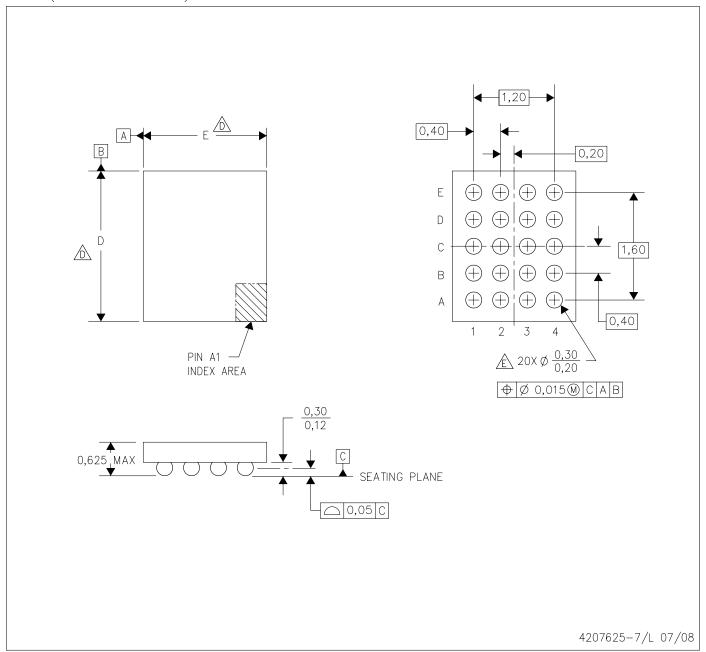

- 1.976 x 1.924mm 20-Pin WCSP Package

#### APPLICATIONS

- **Mobile and Smart Phones**

- **MP3 Players**

- **Handheld Devices**

#### DESCRIPTION

The bq24152 is a compact, flexible, high-efficiency, USB-friendly switch-mode charge management device for single-cell Li-ion and Li-polymer batteries used in a wide range of portable applications. The charge parameters can be programmed through an I<sup>2</sup>C interface. The bq24152 integrates a synchronous PWM controller, power MOSFETs, input current high-accuracy current and voltage regulation, and charge termination, into a small WCSP package.

The bq24152 charges the battery in three phases: conditioning, constant current and constant voltage. The input current is automatically limited to the value set by the host. Charge is terminated based on user-selectable minimum current level. A safety timer with reset control provides a safety backup for I2C interface. During normal operation, automatically restarts the charge cycle if the battery voltage falls below an internal threshold and automatically enters sleep mode or high impedance mode when the input supply is removed. The charge status is reported to the host using the I<sup>2</sup>C interface.

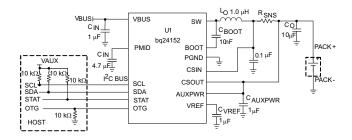

#### Typical Application Circuit

I2C is a trademark of Philips Electronics.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **DESCRIPTION CONTINUED**

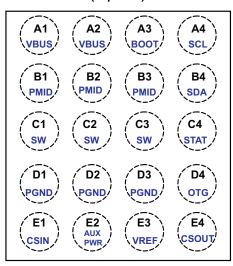

During the charging process, the bq24152 monitors its junction temperature  $(T_J)$  and reduces the charge current once  $T_J$  increases to approximately 125°C. To support USB OTG device, bq24152 provides VBUS (approximately 5.05V) by boosting the battery voltage. The bq24152 is available in 20-pin WCSP package.

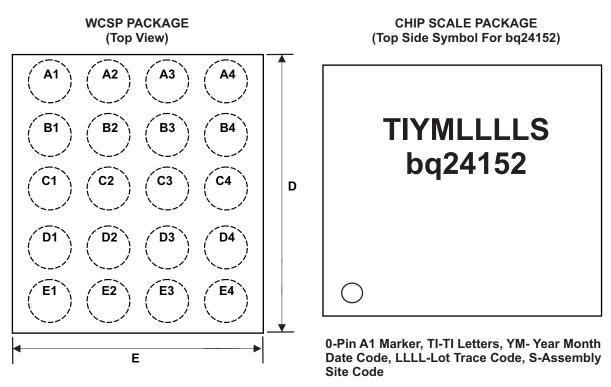

#### WCSP PACKAGE (Top View)

#### **TERMINAL FUNCTIONS**

| TE     | ERMINAL    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|--------|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME   | NO.        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| CSOUT  | E4         | I   | Battery voltage and current sense input. Bypass it with a ceramic capacitor (minimum $0.1~\mu F$ ) to PGND if there are long inductive leads to battery.                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| VBUS   | A1, A2     | I   | Charger input voltage. Bypass it with a 1-µF ceramic capacitor from VBUS to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| PMID   | B1, B2, B3 | 0   | Connection point between reverse blocking MOSFET and high-side switching MOSFET. Bypass it with a minimum of 3.3-μF capacitor from PMID to PGND.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SW     | C1, C2, C3 | 0   | Internal switch to output inductor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| воот   | А3         | 0   | Boot-strapped capacitor for the high-side MOSFET gate driver. Connect a 10-nF ceramic capacitor (voltage rating above 10 V) from BOOT pin to SW pin.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| PGND   | D1, D2, D3 |     | Power ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

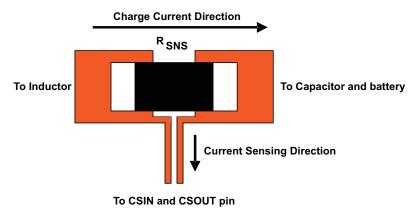

| CSIN   | E1         | I   | Charge current-sense input. Battery current is sensed via the voltage drop across an external sense resistor. A 0.1-µF ceramic capacitor to PGND is required.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| SCL    | A4         | I   | I <sup>2</sup> C interface clock. Open drain output, connect a 10-kΩ pullup resistor                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| SDA    | B4         | I/O | I <sup>2</sup> C interface data. Open drain output, connect a 10-kΩ pullup resistor                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| STAT   | C4         | 0   | Charge status pin. Pull low when charge in progress. Open drain for other conditions. During faults, a 128µS pulse is sent out. STAT pin can be disabled by the EN_STAT bit in control register. STAT can be used to drive a LED or communicate with a host processor.                                                                                                                                                                                                                                                            |  |  |

| VREF   | E3         | 0   | Internal bias regulator voltage. Connect a 1-μF ceramic capacitor from this output to PGND. External load on VREF is not allowed.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| AUXPWR | E2         | I   | Auxiliary power supply, connected to the battery pack to provide power in high-impedance mode. Bypass it with a 1-µF ceramic capacitor from this pin to PGND.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| OTG    | D4         | ı   | Boost mode enable control or input current limiting selection pin. When OTG is in active status, bq24152 is forced to operate in boost mode. It has higher priority over I <sup>2</sup> C control and can be disabled through control register. The logic voltage level at OTG active status can also be controlled. At POR, the OTG pin is default to be used as the input current limiting selection pin. When OTG = High, lin – limit = 500 mA and when OTG = Low, lin – limit = 100 mA, see the Control Register for details. |  |  |

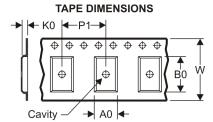

#### ORDERING INFORMATION(1)

| Part NO.    | Part NO. MARKING |               | QUANTITY |  |

|-------------|------------------|---------------|----------|--|

| bq24152YFFR | bq24152          | Tape and Reel | 3000     |  |

| bq24152YFFT | bq24152          | Tape and Reel | 250      |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

# **DISSIPATION RATINGS**(1)

| PACKAGE     | $R_{	heta JA}$         | R <sub>θJC</sub> | T <sub>A</sub> ≤ 25°C<br>POWER RATING | DERATING FACTOR<br>T <sub>A</sub> > 25°C |

|-------------|------------------------|------------------|---------------------------------------|------------------------------------------|

| WSCP-20 (1) | 185°C/W <sup>(2)</sup> | 1.57°C/W         | 0.54 W                                | 0.0054 W/°C                              |

<sup>(1)</sup> Maximum power dissipation is a function of  $T_J(max)$ ,  $R\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = [T_J(max) - T_A] / R\theta_{JA}$ .

#### ABSOLUTE MAXIMUM RATINGS(1)

over operating free-air temperature range (unless otherwise noted)

|                  |                                                 |                                                                   | VALUE      | UNIT |

|------------------|-------------------------------------------------|-------------------------------------------------------------------|------------|------|

| V <sub>SS</sub>  | Supply voltage range (with respect to PGND)     | VBUS                                                              | -0.3 to 20 | V    |

| VI               | Input voltage range (with respect to and PGND)  | SCL, SDA, OTG, CSIN, CSOUT, AUXPWR                                | -0.3 to 7  | V    |

|                  |                                                 | PMID, STAT                                                        | -0.3 to 20 | V    |

| Vo               | Output voltage range (with respect to and PGND) | VREF                                                              | 6.5        | V    |

|                  |                                                 | SW, BOOT                                                          | -0.7 to 20 | V    |

|                  | Voltage difference between C                    | SIN and CSOUT inputs (V <sub>(CSIN)</sub> -V <sub>(CSOUT)</sub> ) | ±7         | V    |

|                  | Output sink                                     | STAT                                                              | 10         | mA   |

| Io               | Output current (average)                        | SW                                                                | 1.25       | Α    |

| T <sub>A</sub>   | Operating free-air temperature                  | e range                                                           | -40 to 85  | °C   |

| $T_{J}$          | Junction temperature                            |                                                                   | -40 to 150 | °C   |

| T <sub>stg</sub> | Storage temperature                             |                                                                   | -65 to 150 | °C   |

| ESD<br>Rating    | Human body model at VBUS,                       | Human body model at VBUS, PMID, STAT <sup>(2)(3)</sup>            |            |      |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. All voltage values are with respect to the network ground terminal unless otherwise noted.

Copyright © 2008, Texas Instruments Incorporated

<sup>(2)</sup> For PCB board with only top trace layer. For PCB board with four layers (top trace layer, buried ground layer, buried signal layer and bottom layer), Rθ<sub>JA</sub> drops to 75.96°C/W

<sup>(2)</sup> The human body model is a 100-pF capacitor discharged through a 1.5-k $\Omega$  resistor into each pin.

<sup>(3)</sup> Other pins pass 2 kV for human body model.

All voltages are with respect to PGND if not specified. Currents are positive into, negative out of the specified terminal.

# RECOMMENDED OPERATING CONDITIONS

|           |                                      | MIN | NOM MAX          | UNIT |

|-----------|--------------------------------------|-----|------------------|------|

| $V_{BUS}$ | Supply voltage, VBUS                 | 4   | 6 <sup>(1)</sup> | V    |

| $T_{J}$   | Operating junction temperature range | 0   | +125             | °C   |

<sup>(1)</sup> The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the BOOT or SW pins. A tight layout minimizes switching noise.

# **ELECTRICAL CHARACTERISTICS**

Circuit of Figure 1, VBUS = 5 V, HZ\_MODE = 0, OPA\_MODE = 0 (charger mode operation),  $T_J = 0$ °C to 125°C,  $T_J = 25$ °C for typical values (unless otherwise noted)

|                        | PARAMETER                                                                                   | TEST CONDITIONS                                                                                                                                      | MIN   | TYP | MAX  | UNIT |

|------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|------|------|

| INPUT CURRE            | NTS                                                                                         |                                                                                                                                                      |       |     |      |      |

|                        |                                                                                             | VBUS > VBUS(min), PWM switching                                                                                                                      |       | 10  |      | mΑ   |

|                        |                                                                                             | VBUS > VBUS(min), PWM NOT switching                                                                                                                  |       |     | 5    |      |

| l(vbus)                | VBUS supply current control                                                                 | $0^{\circ}$ C < T <sub>J</sub> < $85^{\circ}$ C, VBUS = 5 V, HZ_MODE = 1, V <sub>(AUXPWR)</sub> > V <sub>(LOWV)</sub> , SCL, SDA, OTG = 0 V or 1.8 V |       |     | 20   | μА   |

|                        |                                                                                             | 0°C < T <sub>J</sub> < 85°C, VBUS = 5 V, HZ_MODE = 1,<br>V <sub>(AUXPWR)</sub> < V <sub>(LOWV)</sub> , 32 S mode, SCL, SDA, OTG<br>= 0 V or 1.8 V    |       |     | 35   | μА   |

| I <sub>lkg</sub>       | Leakage current from battery to VBUS pin                                                    | 0°C < T <sub>J</sub> < 85°C, V <sub>(AUXPWR)</sub> = 4.2 V, High impedance mode                                                                      |       |     | 5    | μΑ   |

|                        | Battery discharge current in High<br>Impedance mode, (CSIN,<br>CSOUT, AUXPWR, SW pins)      | impedance mode                                                                                                                                       |       | 20  | μА   |      |

| VOLTAGE REC            | GULATION                                                                                    |                                                                                                                                                      |       |     |      |      |

| V <sub>(OREG)</sub>    | Output charge voltage                                                                       | Operating in voltage regulation, programmable                                                                                                        | 3.5   |     | 4.44 | V    |

|                        | Valtage regulation accuracy                                                                 | T <sub>A</sub> = 25°C                                                                                                                                | -0.5% |     | 0.5% |      |

|                        | Voltage regulation accuracy                                                                 |                                                                                                                                                      |       | ±1% |      |      |

| CURRENT REC            | GULATION (FAST CHARGE)                                                                      |                                                                                                                                                      |       |     |      |      |

| I <sub>O(CHARGE)</sub> | Output charge current                                                                       | $V_{(LOWV)} \le V_{(AUXPWR)} < V_{(OREG)}, VBUS > V_{(SLP)},$ $R_{(SNS)} = 68 \text{ m}\Omega \text{ Programmable}$                                  | 550   |     | 1250 | mA   |

|                        | Regulation accuracy for charge                                                              | 20 mV ≤ V <sub>(IREG)</sub> ≤ 40 mV                                                                                                                  | -5%   |     | 5%   |      |

|                        | current across $R_{(SNS)}$<br>$V_{(IREG)} = I_{O(CHARGE)} \times R_{(SNS)}$                 | 40 mV < V <sub>(IREG)</sub>                                                                                                                          | -3%   |     | 3%   |      |

| WEAK BATTE             | RY DETECTION                                                                                |                                                                                                                                                      |       |     |      |      |

| V <sub>(LOWV)</sub>    | Weak battery voltage threshold                                                              | Programmable                                                                                                                                         | 3.4   |     | 3.7  | V    |

| (LOVVV)                | Weak battery voltage accuracy                                                               | 3 **                                                                                                                                                 | -5%   |     | 5%   |      |

|                        | Hysteresis for V <sub>(LOWV)</sub>                                                          | Battery voltage falling                                                                                                                              |       | 100 |      | mV   |

|                        | Deglitch time for weak battery threshold                                                    | Rising voltage, 2 mV overdrive, t <sub>RISE</sub> = 100 ns                                                                                           |       | 30  |      | ms   |

| OTG PIN LOGI           | C LEVEL                                                                                     |                                                                                                                                                      |       |     |      |      |

| V <sub>IL</sub>        | Input low threshold level                                                                   |                                                                                                                                                      |       |     | 0.4  | V    |

| V <sub>IH</sub>        | Input high threshold level                                                                  |                                                                                                                                                      | 1.3   |     |      | V    |

| CHARGE TERI            | MINATION DETECTION                                                                          |                                                                                                                                                      |       |     |      |      |

| I <sub>(TERM)</sub>    | Termination charge current                                                                  | $V_{(AUXPWR)} > V_{(OREG)} - V_{(RCH)},$<br>VBUS > $V_{(SLP)}$ , $R_{(SNS)} = 68 \text{ m}\Omega$ Programmable                                       | 50    |     | 400  | mA   |

|                        | Deglitch time for charge termination                                                        | Both rising and falling, 2 mV overdrive, t <sub>RISE</sub> , t <sub>FALL</sub> = 100 ns                                                              |       | 30  |      | ms   |

|                        | Voltage regulation accuracy for                                                             | 3 mV ≤ V <sub>(IREG_TERM)</sub> < 20 mV                                                                                                              | -25%  |     | 25%  |      |

|                        | termination current across $R_{(SNS)}$<br>$V_{(IREG\_TERM)} = I_{O(TERM)} \times R_{(SNS)}$ | 20 mV ≤ V <sub>(IREG_TERM)</sub> ≤ 40 mV                                                                                                             | -5%   |     | 5%   |      |

| INPUT POWER            | SOURCE DETECTION                                                                            |                                                                                                                                                      |       |     |      |      |

|                        | Input voltage lower limit                                                                   | Input power source detection                                                                                                                         | 3.6   | 3.8 | 4    | V    |

| V <sub>IN</sub> (min)  | Deglitch time for VBUS rising above V <sub>IN</sub> (min)                                   | Rising voltage, 2 mV overdrive, t <sub>RISE</sub> = 100 ns                                                                                           |       | 30  |      | ms   |

|                        | Hysteresis for V <sub>IN</sub> (min)                                                        | Input voltage rising                                                                                                                                 | 100   |     | 200  | mV   |

| t <sub>INT</sub>       | Detection Interval                                                                          | Input power source detection                                                                                                                         |       | 2   |      | S    |

# **ELECTRICAL CHARACTERISTICS (continued)**

Circuit of Figure 1, VBUS = 5 V, HZ\_MODE = 0, OPA\_MODE = 0 (charger mode operation),  $T_J$  = 0°C to 125°C,  $T_J$  = 25°C for typical values (unless otherwise noted)

|                            | PARAMETER                                                             | TEST CONDITION                                                                             | NS .                    | MIN  | TYP   | MAX  | UNIT    |

|----------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------|------|-------|------|---------|

| INPUT CURRE                | NT LIMITING                                                           |                                                                                            | ,                       |      |       | '    |         |

|                            |                                                                       | I <sub>IN</sub>                                                                            | = 100 mA                | 88   | 93    | 98   | mA      |

| I <sub>IN</sub>            | Input current limiting threshold                                      | USB charge mode                                                                            | = 500 mA                | 450  | 475   | 500  |         |

| VREF BIAS RE               | GULATOR                                                               | 1                                                                                          |                         |      |       |      |         |

| V <sub>ref</sub>           | Internal bias regulator voltage                                       | VBUS >V <sub>IN</sub> (min) or V <sub>(AUXPWR)</sub> > V<br>I(VREF) = 1 mA, C(VREF) = 1 μI | ( <sub>(BAT)</sub> min, | 2    |       | 6.5  | V       |

|                            | V <sub>ref</sub> output short current limit                           |                                                                                            |                         |      | 30    |      | mA      |

|                            | Voltage from BOOT pin to SW pin                                       | During charge or boost operation                                                           | ı                       |      |       | 6.5  | V       |

| BATTERY REC                | HARGE THRESHOLD                                                       |                                                                                            |                         |      |       |      |         |

| V <sub>(RCH)</sub>         | Recharge threshold voltage                                            | Below V <sub>(OREG)</sub>                                                                  |                         | 100  | 120   | 150  | mV      |

|                            | Deglitch time                                                         | V <sub>(AUXPWR)</sub> decreasing below thres<br>t <sub>FALL</sub> = 100ns, 10 mV overdrive | shold,                  |      | 130   |      | ms      |

| STAT OUTPUT                | ·s                                                                    |                                                                                            |                         |      |       |      |         |

|                            | Low-level output saturation voltage, STAT                             | I <sub>O</sub> = 10 mA, sink current                                                       |                         |      |       | 0.4  | V       |

| V <sub>OL(STAT)</sub>      | High-level leakage current for STAT                                   | Voltage on STAT pin is 5 V                                                                 |                         |      |       | 1    | μΑ      |

| I <sup>2</sup> C BUS LOGIC | LEVELS AND TIMING CHARACTERI                                          | STICS                                                                                      |                         |      |       |      |         |

| V <sub>OL</sub>            | Output low threshold level                                            | I <sub>O</sub> = 10 mA, sink current                                                       |                         |      |       | 0.4  | V       |

| V <sub>IL</sub>            | Input low threshold level                                             | 10 = 10 m/t, dime deficite                                                                 |                         |      |       | 0.4  | V       |

| V <sub>IH</sub>            | Input high threshold level                                            |                                                                                            |                         | 1.2  |       | 0    | V       |

|                            | Input bias current                                                    | V <sub>(pull-up)</sub> = 1.8 V, SDA and SCL                                                |                         | 1.2  |       | 1    | μA      |

| I <sub>(BIAS)</sub>        | SCL clock frequency                                                   | V <sub>(pull-up)</sub> = 1.0 V, SDA and SOL                                                |                         |      |       | 3.4  | MHz     |

| BATTERY DET                | • • • • • • • • • • • • • • • • • • • •                               |                                                                                            |                         |      |       | 3.4  | IVII IZ |

| BATTERT DET                |                                                                       | Desire ofter termination datasted                                                          |                         |      |       |      |         |

| I <sub>(DETECT)</sub>      | Battery detection current before charge done (sink current) (1)       | Begins after termination detected $V_{(AUXPWR)} \le V_{(OREG)}$                            | ,                       |      | -0.45 |      | mA      |

|                            | Battery detection time                                                |                                                                                            |                         |      | 262   |      | ms      |

| SLEEP COMPA                |                                                                       |                                                                                            |                         |      |       |      |         |

| $V_{(SLP)}$                | Sleep-mode entry threshold,<br>V <sub>BUS</sub> - V <sub>AUXPWR</sub> | $2.3 \text{ V} \leq \text{V}_{(AUXPWR)} \leq \text{V}_{(OREG)}, \text{V}_{BUS}$            | s falling               | +0.0 | +0.04 | +0.1 | V       |

|                            | Sleep-mode exit hysteresis                                            | $2.3 \text{ V} \leq V_{(AUXPWR)} \leq V_{(OREG)}$                                          |                         | 40   | 100   | 160  | mV      |

| $V_{(SLP\_EXIT)}$          | Deglitch time for VBUS rising above $V_{(SLP)} + V_{(SLP\_EXIT)}$     | Rising voltage, 2-mV overdrive, t                                                          | RISE = 100ns            |      | 30    |      | ms      |

| UNDERVOLTA                 | GE LOCKOUT                                                            |                                                                                            |                         |      |       |      |         |

| UVLO                       | IC active threshold voltage                                           | VBUS rising                                                                                |                         | 3.05 | 3.3   | 3.55 | V       |

| UVLO <sub>(HYS)</sub>      | IC active hysteresis                                                  | VBUS falling from above UVLO                                                               |                         | 120  | 150   |      | mV      |

| PWM                        |                                                                       |                                                                                            |                         |      |       |      |         |

|                            | Internal top reverse blocking MOSFET on-resistance                    | I <sub>IN(LIMIT)</sub> = 500 mA, Measured from PMID                                        | m VBUS to               |      | 180   | 250  |         |

|                            | Internal top N-channel Switching MOSFET on-resistance                 | Measured from PMID to SW                                                                   |                         |      | 120   | 250  | mΩ      |

|                            | Internal bottom N-channel MOSFET on-resistance                        | Measured from SW to PGND                                                                   |                         |      | 150   | 200  |         |

| f <sub>(OSC)</sub>         | Oscillator frequency                                                  | ency                                                                                       |                         |      | 3     |      | MHz     |

|                            | Frequency accuracy                                                    |                                                                                            |                         | -10% |       | 10%  |         |

| D <sub>(MAX)</sub>         | Maximum duty cycle                                                    |                                                                                            |                         |      | 99.5% |      |         |

| D <sub>(MIN)</sub>         | Minimum duty cycle                                                    |                                                                                            |                         | 0    |       |      |         |

| (vina)                     | Synchronous mode transition current threshold (2)                     | Low side MOSFET cycle by cycle                                                             | e current sensing       |      | 100   |      | mA      |

<sup>(1)</sup> Negative charge current means the charge current flows from the battery to charger (discharging battery).

<sup>(2)</sup> Bottom N-channel MOSFET always turns on for ≈60 ns and then turns off if current is too low.

# **ELECTRICAL CHARACTERISTICS (continued)**

Circuit of Figure 1, VBUS = 5 V, HZ\_MODE = 0, OPA\_MODE = 0 (charger mode operation),  $T_J = 0$ °C to 125°C,  $T_J = 25$ °C for typical values (unless otherwise noted)

|                        | PARAMETER                                                                | TEST CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNIT               |

|------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|--------------------|

| BOOST MODE             | OPERATION FOR VBUS (OPA_MODI                                             | E = 1, HZ_MODE = 0)                                                                       |      |      |      |                    |

| V <sub>(BUS_B)</sub>   | Boost output voltage (to pin VBUS)                                       | 2.5 V < V <sub>(AUXPWR)</sub> < 4.5 V, Open loop                                          |      | 5.05 |      | V                  |

|                        | Boost output voltage accuracy                                            | Including line and load regulation                                                        |      | ±3%  |      |                    |

| I <sub>(BO)</sub>      | Maximum output current for boost                                         | V <sub>(BUS_B)</sub> = 5.05 V, 2.5 V < V <sub>(AUXPWR)</sub> < 4.5 V                      | 200  |      |      | mA                 |

| I <sub>(BLIMIT)</sub>  | Cycle by cycle current limit for boost                                   | V <sub>(BUS_B)</sub> = 5.05 V, 2.5 V < V <sub>(AUXPWR)</sub> < 4.5 V                      |      | 1    |      | А                  |

| VBUS <sub>(OVP)</sub>  | Overvoltage protection threshold for boost (VBUS pin)                    | Threshold over VBUS to turn off converter during boost                                    | 5.8  | 6    | 6.2  | V                  |

| (211)                  | VBUS <sub>(OVP)</sub> hysteresis                                         | VBUS falling from above VBUS <sub>(OVP)</sub>                                             |      | 125  |      | mV                 |

| V <sub>(BAT)</sub> MAX | Maximum battery voltage for boost (CSOUT pin)                            | V <sub>(CSOUT)</sub> rising edge during boost                                             | 4.75 | 4.9  | 5.05 | V                  |

| (=)                    | V <sub>(BAT)</sub> MAX hysteresis                                        | V <sub>(CSOUT)</sub> falling from above VBATMAX                                           |      | 200  |      | mV                 |

| V <sub>(BAT)</sub> MIN | Minimum battery voltage for                                              | During boosting                                                                           |      | 2.5  |      | V                  |

|                        | boost (AUXPWR pin)                                                       | Before boost starts                                                                       |      | 2.9  | 3.05 | V                  |

|                        | Boost output resistance at<br>high-impedance mode (From<br>VBUS to PGND) | HZ_MODE = 1                                                                               | 165  |      |      | kΩ                 |

| PROTECTION             |                                                                          |                                                                                           |      |      |      |                    |

| V <sub>(OVP-IN)</sub>  | Input VBUS OVP threshold voltage                                         | Threshold over VBUS to turn off converter during charge                                   | 6.3  | 6.5  | 6.7  | V                  |

| (211 111)              | V <sub>(OVP_IN)</sub> hysteresis                                         | VBUS falling from above V <sub>(OVP_IN)</sub>                                             |      | 140  |      | mV                 |

| V <sub>(OVP)</sub>     | Battery OVP threshold voltage                                            | V <sub>(CSOUT)</sub> threshold over V <sub>(OREG)</sub> to turn off charger during charge | 110  | 117  | 121  | %V <sub>(ORE</sub> |

| (= ,                   | V <sub>(OVP)</sub> hysteresis                                            | Lower limit for V <sub>(CSOUT)</sub> falling from above V <sub>(OVP)</sub>                |      | 11   |      | G)                 |

| I <sub>(LIMIT)</sub>   | Cycle-by-cycle current limit for charge                                  | Charge mode operation                                                                     | 1.5  | 2.3  | 3    | А                  |

| V                      | Short-circuit voltage threshold                                          | V <sub>(AUXPWR)</sub> falling                                                             | 1.9  | 2    | 2.1  | V                  |

| $V_{(SHORT)}$          | V <sub>(SHORT)</sub> hysteresis                                          | V <sub>(AUXPWR)</sub> rising from below V <sub>(SHORT)</sub>                              |      | 100  |      | mV                 |

| I <sub>(SHORT)</sub>   | Short-circuit current                                                    | V <sub>(AUXPWR)</sub> ≤ V <sub>(SHORT)</sub>                                              | 5    | 10   | 15   | mA                 |

| T <sub>(SHTDWN)</sub>  | Thermal trip                                                             |                                                                                           |      | 165  | -    |                    |

|                        | Thermal hysteresis                                                       |                                                                                           |      | 10   |      | °C                 |

| T <sub>(CF)</sub>      | Thermal regulation threshold <sup>(3)</sup>                              | Charge current begins to reduce                                                           |      | 120  |      | 1                  |

| T <sub>(32S)</sub>     | Time constant for the 32 second timer                                    | 32 Second mode                                                                            | 12   | 32   |      | s                  |

<sup>(3)</sup> Verified by design

SLUS847-JUNE 2008

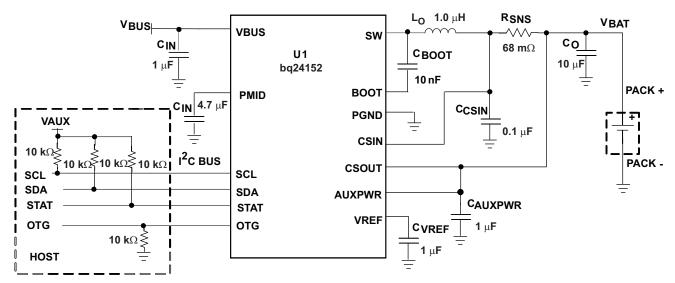

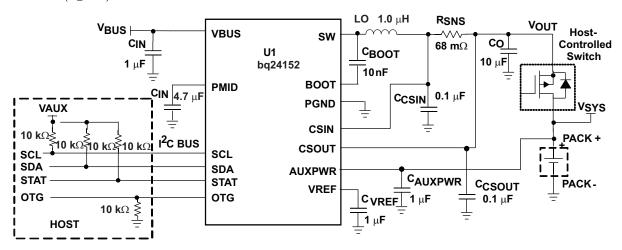

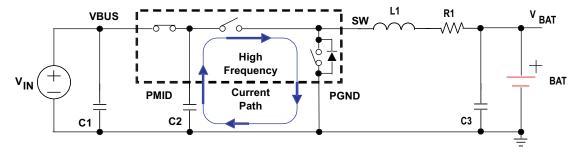

### TYPICAL APPLICATION CIRCUITS

VBUS = 5 V,  $I_{(IN\_LIMIT)}$  = 500 mA,  $I_{(CHARGE)}$  = 750 mA, VBAT = 3.5 V to 4.44 V (adjustable), Safety Timer = 32 minutes or 32 seconds.

Figure 1. I<sup>2</sup>C Controlled 1-Cell Charger Application Circuit

VBUS = 5 V, I<sub>(IN LIMIT)</sub> = 500 mA, V<sub>OUT</sub> = 3.5 V to 4.44 V (adjustable), Safety Timer = 32 minutes or 32 seconds.

Figure 2. I<sup>2</sup>C Controlled 1-Cell Pre-Regulator Application

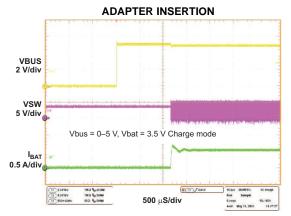

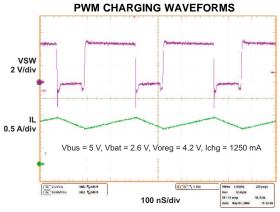

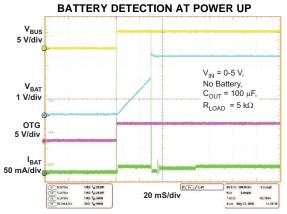

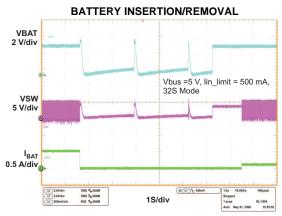

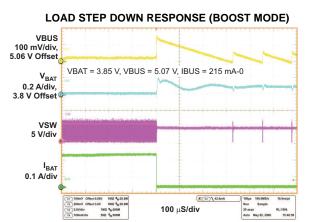

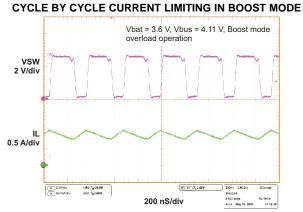

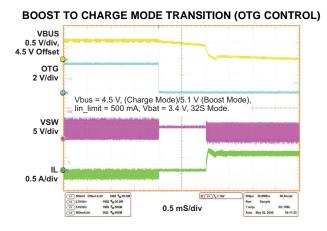

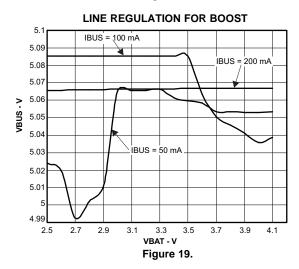

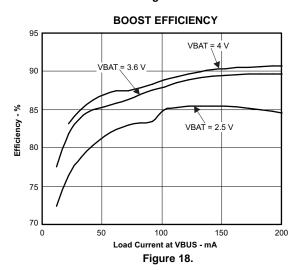

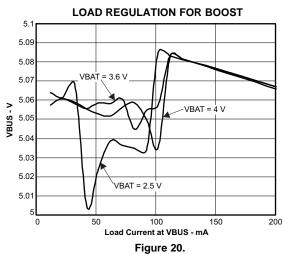

#### TYPICAL CHARACTERISTICS

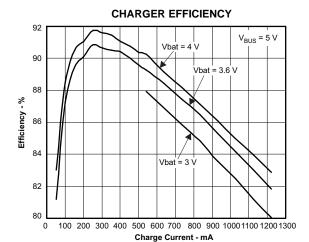

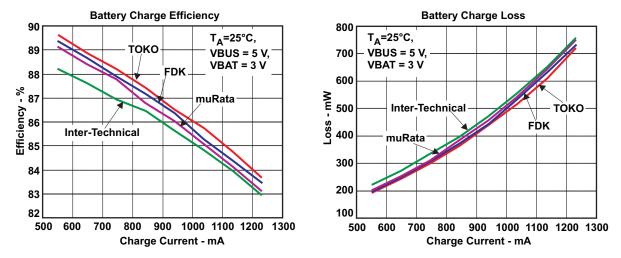

Using circuit shown in Figure 1, T<sub>A</sub> = 25°C, unless otherwise specified.

Figure 3.

Figure 5.

Figure 7.

Figure 4.

Figure 6.

Figure 8.

# **TYPICAL CHARACTERISTICS (continued)**

Figure 9.

Figure 11.

Figure 10.

Figure 12.

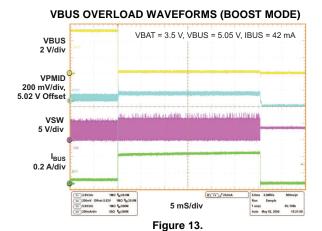

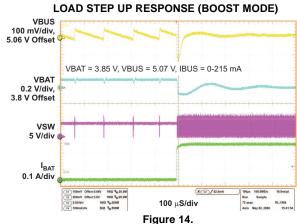

rigure 14.

# TEXAS INSTRUMENTS

# **TYPICAL CHARACTERISTICS (continued)**

Figure 15.

Figure 16.

Figure 17.

www.ti.com

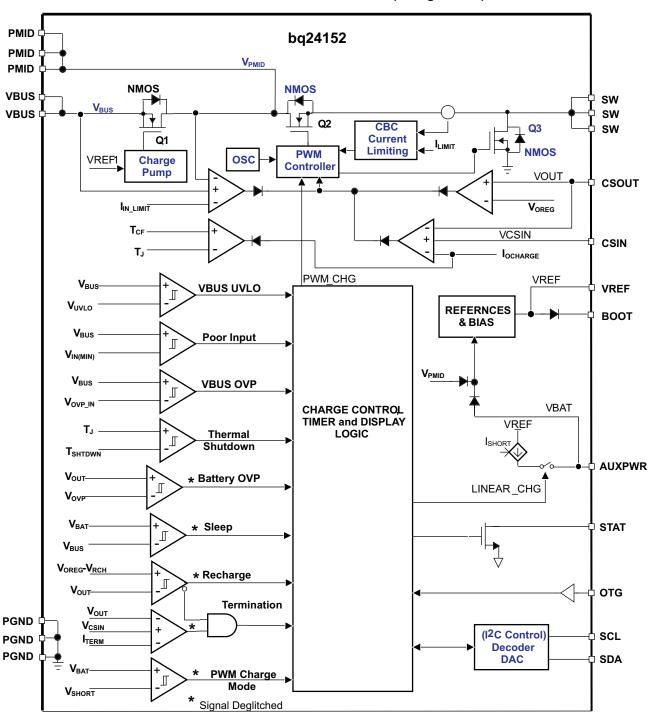

#### **FUNCTIONAL BLOCK DIAGRAM (Charge Mode)**

Figure 21. Function Block Diagram of bq24152 in Charge Mode

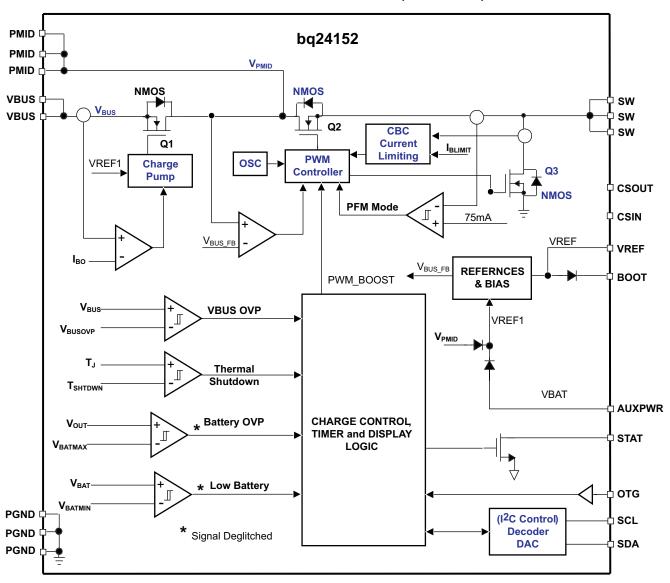

# **FUNCTIONAL BLOCK DIAGRAM (Boost Mode)**

Figure 22. Function Block Diagram of bq24152 in Boost Mode

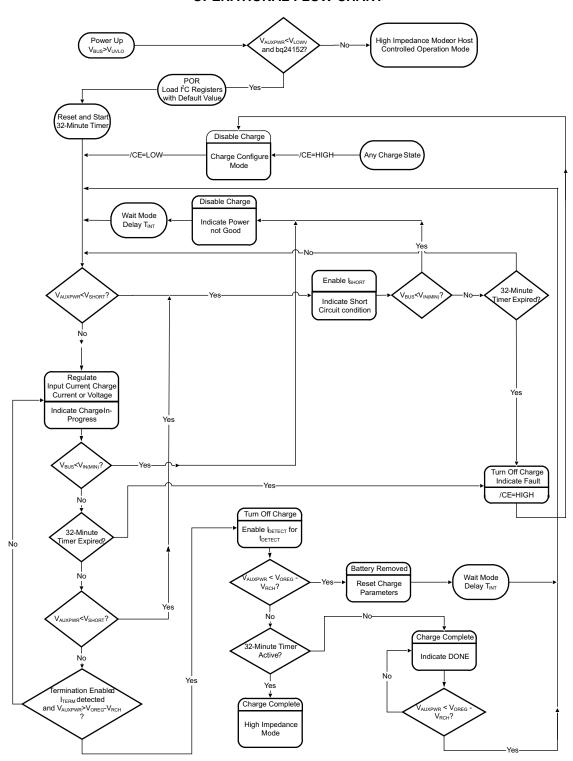

# **OPERATIONAL FLOW CHART**

Figure 23. Operational Flow Chart of bq24152 in Charge Mode

#### **DETAILED FUNCTIONAL DESCRIPTION**

For a current limited power source, such as a USB host or hub, the high efficiency converter is critical in fully using the input power capacity and charging the battery. Due to the high efficiency in a wide range of the input voltage and battery voltage, the switching mode charger is a good choice for high speed charging with less power loss and better thermal management.

The bq24152 is a highly integrated synchronous switch-mode charger with reverse boost function for USB OTG support, featuring integrated MOSFETs and small external components, targeted at extremely space-limited portable applications powered by 1-cell Li-lon or Li-polymer battery pack.

The bq24152 usually has three operation modes: charge mode, boost mode, and high impedance mode. In charge mode, the bq24152 supports a precision Li-ion or Li-polymer charging system for single-cell applications. In boost mode, bq24152 boosts the battery voltage to VBUS for powering attached OTG devices. In high impedance mode, the bq24152 stops charging or boosting and operates in a mode with low current from VBUS or battery, to effectively reduce the power consumption when the portable device in standby mode. Through the proper control, bq24152 can achieve the smooth transition among different operation modes.

#### **CHARGE MODE OPERATION**

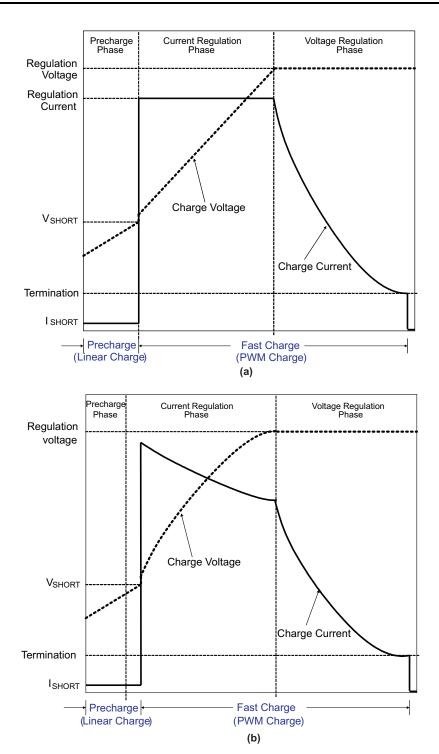

#### Charge Profile

In charge mode, bq24152 has four control loops to regulate input current, charge current, charge voltage and device junction temperature, as shown in Figure 21. During the charging process, all four loops are enabled and the one that is dominant will take over the control. The bq24152 supports a precision Li-ion or Li-polymer charging system for single-cell applications. Figure 24(a) indicates a typical charge profile without input current regulation loop and it is similar to the traditional CC/CV charge curve, while Figure 24(b) shows a typical charge profile when input current limiting loop is dominant during the constant current mode, and in this case the charge current is higher than the input current so the charge process is faster than the linear chargers. For bq24152, the input current limits, the charge current, termination current, and charge voltage are all programmable using I<sup>2</sup>C interface.

Figure 24. Typical Charging Profile of bq24152 for (a) without Input Current Limit, and (b) with Input Current Limit

#### **PWM Controller in Charge Mode**

The bq24152 provides an integrated, fixed 3-MHz frequency voltage-mode controller with Feed-Forward function to regulate charge current or voltage. This type of controller is used to help improve line transient response, thereby, simplifying the compensation network used for both continuous and discontinuous current conduction operation. The voltage and current loops are internally compensated using a Type-III compensation scheme that provides enough phase margin for stable operation, allowing the use of small ceramic capacitors with low ESR. There is a 0.5-V offset on the bottom of the PWM ramp to allow the device to operate between 0% to 99.5% duty cycles.

The bq24152 has two back to back common-drain N-channel MOSFETs at the high side and one N-channel MOSFET at low side. An input N-MOSFET (Q1) prevents battery discharge when VBUS is lower than VAUXPWR. The second high-side N-MOSFET (Q2) behaves as the switching control switch (see Figure 21). A charge pump circuit is used to provide gate drive for Q1, while a boot strap circuit with external boot-strap capacitor is used to boost up the gate drive voltage for Q2.

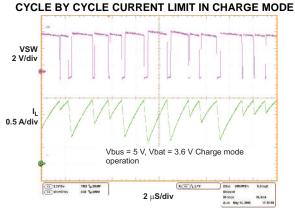

Cycle-by-cycle current limit is sensed through the internal sense MOSFETs for Q2 and Q3. The threshold for Q2 is set to a nominal 1.9-A peak current. The low-side MOSFET (Q3) also has a current limit that decides if the PWM Controller will operate in synchronous or non-synchronous mode. This threshold is set to 100mA and it turns off the low-side N-channel MOSFET (Q3) before the current reverses, preventing the battery from discharging. Synchronous operation is used when the current of the low-side MOSFET is greater than 100mA to minimize power losses.

#### **Battery Charging Process**

At the beginning of precharge, while battery voltage is below the  $V_{(SHORT)}$  threshold, the bq24152 applies a short-circuit current,  $I_{(SHORT)}$ , to the battery.

When the battery voltage is above  $V_{(SHORT)}$  and below  $V_{(OREG)}$ , the charge current ramps up to fast charge current,  $I_{O(CHARGE)}$ , or a charge current that corresponds to the input current of  $I_{(IN\_LIMIT)}$ . The slew rate for fast charge current is controlled to minimize the current and voltage over-shoot during transient. Both the input current limit (default at 100 mA), IIN\_LIMIT, and fast charge current,  $I_{O(CHARGE)}$ , can be set by the host. Once the battery voltage is close to the regulation voltage,  $V_{(OREG)}$ , the charge current is tapered down as shown in Figure 24. The voltage regulation feedback occurs by monitoring the battery-pack voltage between the CSOUT and PGND pins. bq24152 is a fixed single-cell voltage version, with adjustable regulation voltage (3.5 V to 4.44 V) programmed through  $I^2C$  interface.

The bq24152 monitors the charging current during the voltage regulation phase. Once the termination threshold, ITERM, is detected and the battery voltage is above the recharge threshold, the bq24152 terminates charge. The termination current level is programmable. To disable the charge current termination, the host can set the charge termination bit (I\_Term) of charge control register to 0, see the I<sup>2</sup>C section for details.

A new charge cycle is initiated when one of the following conditions is detected:

- The battery voltage falls below the  $V_{(OREG)} V_{(RCH)}$  threshold.

- VBUS Power-on reset (POR), if battery voltage is below the V<sub>(LOWV)</sub> threshold.

- CE bit toggle or RESET bit is set (host controlled)

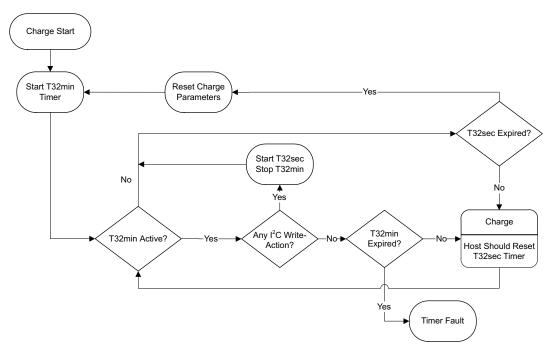

#### Safety Timer in Charge Mode

At the beginning of charging process, the bq24152 starts a 32-minute timer (T32min) that can be stopped by any write-action performed by host through I<sup>2</sup>C interface. Once the 32-minute timer is stopped, a 32-second timer (T32sec) is automatically started. The 32-second timer can be reset by host using I<sup>2</sup>C interface. Writing "1" to reset bit of TMR\_RST in control register resets the 32-second timer and TMR\_RST is automatically set to "0" after the 32-second timer is reset. If the 32-second timer expires, the charge is terminated and charge parameters are reset to default values. Then the 32-minute timer starts and the charge resumes.

During normal charging process, the bq24152 is normally in 32-second mode with host control, and 32-minute mode without host control using  $I^2C$  interface. The process repeats until the battery is fully charged. If the 32-minute timer expires, bq24152 turns off the charger and enunciates FAULT on the STATx bits of status register. This function prevents battery over charge if the host fails to reset the safety timer. The safety timer flow chart is shown in Figure 25. Fault condition is cleared by POR and fault status bits can only be updated after the status bits are read out by the host.

Figure 25. Timer Flow Chart for bq24152 in Charge Mode

# **USB Friendly Boot-Up Sequence**

At power on reset (POR) of VBUS, if the battery voltage is above the weak battery threshold,  $V_{LOWV}$ , bq24152 will operate in a mode dictated by the  $I^2C$  control registers. On the other hand, if the battery voltage is below  $V_{LOWV}$  and the host control through  $I^2C$  interface is lost (32 minute mode), bq24152 will reset all  $I^2C$  registers with default values and enable the charger with an input current limit dictated by the OTG pin voltage level until the host programs the  $I^2C$  registers. During this period, the input current limit is 100 mA when the voltage level of OTG pin is Low; while the input current limit is 500 mA when the voltage level of OTG pin is high. This feature could quickly revive the deeply discharged cell. The charge process continues even the battery is charged to the regulation voltage (default at 3.54 V) since termination is disabled by default. In another case, if the battery voltage is below  $V_{LOWV}$  but the host control using  $I^2C$  interface is available (32 second mode), bq24152 will operate in a mode dictated by control registers.

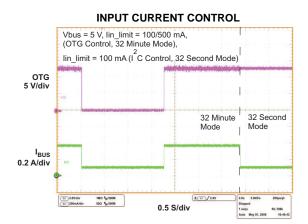

#### Input Current Limiting

To maximize the charge rate of bq24152 without overloading the USB port, the input current for bq24152 can be limited to 100mA or 500mA which is programmed in the control register or OTG pin. Once the input current reaches the input current limiting threshold, the charge current is reduced to keep the input current from exceeding the programmed threshold. For bq14150, the default input current limit is controlled by the OTG pin at VBUS power on reset when  $V_{(AUXPWR)}$  is lower than  $V_{(LOWV)}$ . The input current sensing resistor and control loop are integrated into bq24152. The input current limit can also be disabled using I<sup>2</sup>C control, see the definition of control register (01H) for details.

#### **Thermal Regulation and Protection**

To prevent overheating the chip during the charging process, the bq24152 monitors the junction temperature,  $T_J$ , of the die and begins to taper down the charge current once  $T_J$  reaches the thermal regulation threshold,  $T_{CF}$ . The charge current is reduced to zero when the junction temperature increases approximately 10°C above  $T_{CF}$ . At any state, if  $T_J$  exceeds  $T_{SHTDWN}$ , bq24152 suspends charging. At thermal shutdown mode, PWM is turned off and all timers are frozen. Charging resumes when  $T_J$  falls below  $T_{SHTDWN}$  by approximately 10°C.

#### Input Voltage Protection in Charge Mode

#### Sleep Mode

The bq24152 enters the low-power sleep mode if the voltage on VBUS pin falls below sleep-mode entry threshold,  $V_{AUXPWR} + V_{SLP}$ , and VBUS is still higher than the poor source detection threshold,  $V_{IN}$ (min). This feature prevents draining the battery during the absence of VBUS. During sleep mode, both the reverse blocking switch Q1 and PWM are turned off.

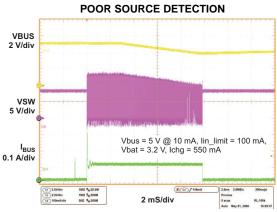

#### Input Source Detection

During the charging process, bq24152 continuously monitors the input voltage, VBUS. If VBUS falls to the low input voltage threshold,  $V_{IN}(min)$ , poor input power source is detected. Under this condition, bq24152 terminates the charge process, waits for a delay time of  $T_{INT}$  and repeats the charging process, as indicated in Figure 23. This unique function provides intelligence to bq24152 and so prevents USB power bus collapsing and oscillation when connecting to a suspended USB port, or a USB-OTG device with low current capability.

#### Input Overvoltage Protection

The bq24152 provides a built-in input over-voltage protection to protect the device and other components against damages if the input voltage (Voltage from VBUS to PGND) goes too high. When an input overvoltage condition is detected, bq24152 turns off the PWM converter, sets fault status bits, and sends out fault pulse in STAT pin. Once VBUS drops below the input overvoltage exit threshold, the fault is cleared and charge process resumes.

### **Battery Protection in Charge Mode**

#### **Output Overvoltage Protection**

The bq24152 provides a built-in overvoltage protection to protect the device and other components against damage if the battery voltage goes too high, as when the battery is suddenly removed. When an overvoltage condition is detected, bq24152 turns off the PWM converter, sets fault status bits and sends out fault pulse in STAT pin. Once  $V_{(CSOUT)}$  drops to the battery overvoltage exit threshold, the fault is cleared and charge process back to normal.

#### **Battery Detection During Normal Charging**

For applications with removable battery packs, the bq24152 provides a battery absent detection scheme to reliably detect insertion or removal of battery packs.

During normal charging process with host control, once the voltage at the AUXPWR pin is above the battery recharge threshold,  $V_{(OREG)} - V_{(RCH)}$ , and the termination charge current is detected, bq24152 turns off the charge and enables a discharge current,  $I_{(DETECT)}$ , for a period of  $t_{DETECT}$ , then checks the battery voltage. If the battery voltage is still above recharge threshold, the battery is present and the charge done is detected. However, if the battery voltage is below battery recharge threshold, the battery is absent. Under this condition, the charge parameters (such as input current limit) are reset to the default values and charge resumes after a delay of  $T_{INT}$ , as shown in Figure 23. This function ensures that the charge parameters are reset whenever the battery is replaced.

#### Power Up Without Battery

When no battery is present, at VBUS power up, bq24152 will charge the output capacitor in short circuit mode (when  $V_{AUXPWR} < V_{SHORT}$ ) or PWM mode (when  $V_{AUXPWR} > V_{SHORT}$ ). Once the output voltage at CSOUT pin is charged to the default regulation voltage (3.54V), the voltage is kept constant until the 32-minute timer expires or the host takes over the control through  $I^2C$  interface. This unique feature makes bq24152 capable of starting the system without battery.

### **Battery Short Protection**

During the normal charging process, if the battery voltage is lower than the short-circuit threshold,  $V_{(SHORT)}$ , the charger operates in short circuit mode with a lower charge rate of  $I_{(SHORT)}$ , as shown in Figure 22.

#### **Charge Status Output, STAT Pin**

The STAT pin is used to indicate operation conditions for bq24152. STAT is pulled low during charging and EN\_STAT bit in control register (00H) is set to "1". Under other conditions, the STAT pin acts as a high impedance (open-drain) output. Under fault conditions, a 128-µs pulse is sent out to notify the host. The status of STAT pin at different operation conditions is summarized in Table 1. The STAT pin can be used to drive an LED or communicate to the host processor.

**Table 1. STAT Pin Summary**

| Charge State                                                                                                                         | STAT                          |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| Charge in progress and EN_STAT = 1                                                                                                   | Low                           |

| Other normal conditions                                                                                                              | Open-drain                    |

| Charge mode faults: Timer fault, sleep mode, VBUS or battery overvoltage, poor input source, VBUS UVLO, no battery, thermal shutdown | 128-μs pulse, then open-drain |

| Boost mode faults: Timer fault, over load, VBUS or battery overvoltage, low battery voltage, thermal shutdown                        | 128-μs pulse, then open-drain |

#### **Control Bits in Charge Mode**

## **CE** Bit (Charge Mode)

The bit of  $\overline{\text{CE}}$  in control register is used to disable or enable the charge process. A low logic level (0) on this bit enables the charge and a high logic level (1) disables the charge.

#### **RESET Bit**

The bit of RESET in control register is used to reset all the charge parameters. Writing '1" to RESET bit resets all the charge parameters to default values and RESET bit is automatically cleared to zero once the charge parameters are reset. It is designed for charge parameter reset before charge starts, and it is not recommended to set the RESET bit when charging or boosting in progress.

#### **OPA Mode Bit**

OPA\_MODE is the operation mode control bit. When OPA\_MODE = 0, the bq24152 charges the related operation modes if HZ\_MODE is set to "0", refer to Table 2 for detail.

**Table 2. Operation Mode Summary**

| OPA_MODE | HZ_MODE | OPERATION MODE                                                                                                                           |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | 0       | Charge (no fault) Charge configure (fault, V <sub>bus</sub> > V <sub>UVLO</sub> ) High impedance (V <sub>bus</sub> < V <sub>UVLO</sub> ) |

| 1        | 0       | Boost (no faults) Any fault go to charge configure mode                                                                                  |

| X        | 1       | High impedance                                                                                                                           |

#### **Boost Mode Operation**

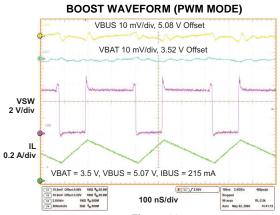

In 32 second mode, when the OTG pin is in active status or the bit of operation mode (OPA\_MODE) at control register is set to 1, the bq24152 operates in boost mode and delivers the power to VBUS from the battery. At normal boost mode, bq24152 converts the battery voltage (2.5 V to 4.5 V) to VBUS-B (about 5.05V) and delivers a current as much as  $I_{(BO)}$  (approximately 200 mA) to support other USB OTG devices connected to the USB connector.

#### **PWM Controller in Boost Mode**

Similar to charge mode operation, in boost mode, the bq24152 provides an integrated, fixed 3 MHz frequency voltage-mode controller to regulate output voltage at PMID pin (VPMID), as shown in Figure 22. The voltage control loop is internally compensated using a Type-III compensation scheme that provides enough phase margin for stable operation with a wide load range and battery voltage range

In boost mode, the input N-MOSFET (Q1) prevents battery discharge when VBUS pin is overloaded. Cycle-by-cycle current limit is sensed through the internal sense MOSFET for Q3. The threshold for Q3 is set to a nominal 1-A peak current. The upper-side MOSFET (Q2) also has a current limit that decides if the PWM Controller will operate in synchronous or non-synchronous mode. This threshold is set to 75 mA and it turns off the high-side N-channel MOSFET (Q2) before the current reverses, preventing the battery from charging. Synchronous operation is used when the current of the high-side MOSFET is greater than 75 mA to minimize power losses.

#### **Boost Start Up**

To prevent the inductor saturation and limit the inrush current, a soft-start control is applied during the boost start up.

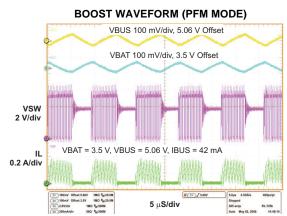

#### PFM Mode at Light Load

In boost mode, the bq24152 operates in pulse skipping mode (PFM mode) to reduce the power loss and improve the converter efficiency at light load condition. During boosting, the PWM converter is turned off once the inductor current is less than 75 mA; and the PWM is turned back on only when the voltage at PMID pin drops to about 99.5% of the rated output voltage. A unique pre-set circuit is used to make the smooth transition between PWM and PFM mode.

#### Safety Timer in Boost Mode

At the beginning of boost operation, the bq24152 starts a 32-second timer that can be reset by host through I<sup>2</sup>C interface. Writing "1" to reset bit of TMR\_RST in the control register resets the 32-second timer and TMR\_RST is automatically set to "0" after the 32-second timer is reset. To keep in boost mode, the host must reset the 32-second timer repeatedly. Once the 32-second timer expires, the bq24152 turns off the boost converter, enunciate the fault pulse in STAT pin and set fault status bits in status register. Fault condition is cleared by POR or host control.

#### Protection in Boost Mode

#### **Output Overvoltage Protection**

The bq24152 provides a built-in overvoltage protection to protect the device and other components against damage if the VBUS voltage goes too high. When an overvoltage condition is detected, the bq24152 turns off the PWM converter, reset OPA\_MODE bit to 0, sets fault status bits, and sends out fault pulse in STAT pin. Once VBUS drops to the normal level, the boost starts after host sets OPA\_MODE to "1", or the OTG pin remains in active status.

#### **Output Overload Protection**

The bq24152 provides a built-in overload protection to prevent the device and battery from damage when VBUS is over loaded. Once over load condition is detected, Q1 operates in linear mode to limit the output current while VPMID keeps in voltage regulation. If the overload condition lasts for more than 30ms, the overload fault is detected. When an overload condition is detected, the bq24152 turns off the PWM converter, reset OPA\_MODE bit to 0, sets fault status bits, and sends out fault pulse in STAT pin. The boost will not start until the host clears the fault register.

#### **Battery Voltage Protection**

During boosting, when battery voltage is above the battery overvoltage threshold,  $V_{(BATMX)}$ , or below the minimum battery voltage threshold,  $V_{(BAT)}$ min, the bq24152 turns off the PWM converter, reset OPA\_MODE bit to 0, sets fault status bits, and sends out fault pulse in STAT pin. Once battery voltage goes back to the normal level, the boost starts after host sets OPA\_MODE to "1", or the OTG pin remains in active status.

#### **STAT Pin Boost Mode**

During normal boosting process, the STAT pin behaves as a high impedance (open-drain) output. Under fault conditions, a 128-µs pulse is sent out to notify the host.

20

#### **High Impedance Mode**

When control bit of HZ-MODE is set to "1" and the OTG pin is not in active status, the bq24152 operates in high impedance mode, with the impedance in VBUS pin higher than 165 k $\Omega$ . In high impedance mode, a crude 32-second timer is enabled when the battery voltage is below V<sub>(LOWV)</sub> to monitor the host control is available or not. If the crude 32 second timer expires, the bq24152 operates in 32 minute mode and the crude 32 second timer is disabled. In 32 minute mode, when VBUS is below UVLO, the bg24152 operates in high impedance mode regardless of the setting of the HZ MODE bit.

#### **Output Inductor and Capacitance Selection Guidelines**

The bq24152 provides internal loop compensation. With this scheme, the best stability occurs when the LC resonant frequency,  $f_0$ , is approximately 40 kHz (20 kHz to 80 kHz). Equation 1 is used to calculate the value of the output inductor, L<sub>OUT</sub>, and output capacitor, C<sub>OUT</sub>.

$$f_{\rm O} = \frac{1}{2\pi \times \sqrt{L_{\rm OUT} \times C_{\rm OUT}}} \tag{1}$$

To reduce the output voltage ripple, a ceramic capacitor with the capacitance between 4.7 μF and 47 μF is recommended for C<sub>OUT</sub>, see the application section for components selection.

#### **Pre-Regulator Application**

Figure 2 shows a typical pre-regulator application that the bg24152 operates as a DC/DC converter, with the termination disabled. The robust internal compensation design ensures the stable operation when the host-controlled switch is turned off. With the input overvoltage protection, output current regulation and high efficiency power conversion, the bq24152 is an ideal choice for pre-regulator used in pulse charging applications.

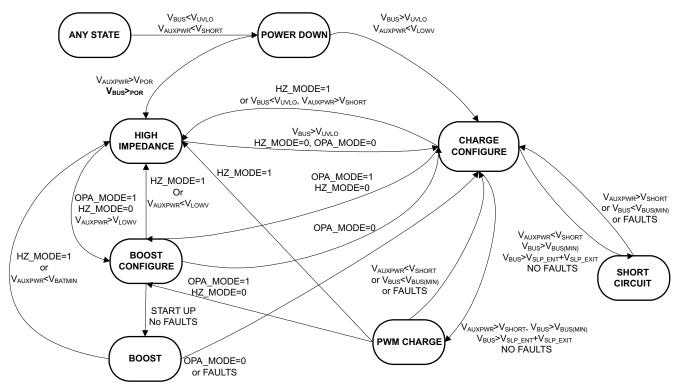

#### State Machine Table and State Diagram

VBUS > UVLO

$V_{(AUXPWR)} > V_{(SHORT)}$

Off

Based on the previously-described operation modes, the definitions of all operation states are shown in Table 3 and Table 4, whereas the relationship among different states is shown in Figure 26.

**CHARGE CONFIGURE** MODE **POWER DOWN SHORT CIRCUIT PWM CHARGE**  $OPA\_MODE = 0$  $OPA\_MODE = 0$  $OPA\_MODE = 0$  $HZ_MODE = 0$  $HZ_MODE = 0$  $HZ_MODE = 0$ **OTG** Inactive **OTGlinactive** OTG Inactive VBUS > UVLO VBUS < VBUS(MIN) VBUS < VBUS(MIN) VBUS < UVLO VBUS < V<sub>(SLP\_ENT)</sub> VBUS < V<sub>(SLP\_ENT)</sub> **IN** Condition VBUS < VBUS(MIN)  $V_{(AUXPWR)} < V_{(SHORT)}$ +V<sub>(SLP\_EXIT)</sub>

V<sub>(AUXPWR)</sub> < V<sub>(SHORT)</sub>

CE = Low +V<sub>(SLP\_EXIT)</sub> V<sub>(AUXPWR)</sub> < V<sub>(SHORT)</sub> CE = Low VBUS < V<sub>(SLP\_ENT)</sub> or CE = HIGH No Faults No Faults OPA MODE = 1 OPA MODE = 1 OPA\_MODE = 1

or HZ MODE = 1

or

VBUS > VBUS(MIN)

VBUS > V<sub>(SLP\_ENT)</sub>

+ V<sub>(SLP\_EXIT)</sub>

or VBUS > UVLO

**OTG** Active

On

or HZ MODE = 1

VBUS < VBUS(MIN)

VBUS < V<sub>(SLP\_ENT)</sub>

or

$V_{(AUXPWR)} < V_{(SHORT)}$ CE = HIGH

or Faults

or OTG Active

On

Table 3. State Machine Table 1 of bq24152

**OUT Condition**

I<sup>2</sup>C

or HZ MODE = 1

VBUS < VBUS(MIN)

VBUS < V<sub>(SLP\_ENT)</sub>

or

$V_{(AUXPWR)} < V_{(SHORT)}$ CE = HIGH

or Faults

or OTG Active

On

Table 4. State Machine Table 2 of bq24152

| MODE          | HIGH IMPEDANCE                                                                                                                                                                                                  | BOOST CONFIGURE                                                                                                                | BOOST                                                                                                                |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| IN Condition  | OPA_MODE = 1 or OTG inactive  VBUS < UVLO, V <sub>(AUXPWR)</sub> > V <sub>(SHORT)</sub> or Boost Configure, V <sub>(AUXPWR)</sub> + V <sub>(LOWV)</sub> or Boost, V <sub>(AUXPWR)</sub> +V <sub>(BAT)</sub> MIN | OPA_MODE = 1 or HZ_MODE = 1 or OTG active V <sub>(AUXPWR)</sub> > V <sub>(LOWV)</sub> Ready To Start Up or Faults During Boost | OPA_MODE = 1 HZ_MODE = 0 or OTG active V <sub>(AUXPWR)</sub> > V <sub>(BAT)</sub> MIN Start Up Finished or No Faults |

| OUT Condition | HZ_MODE = 0, OPA_MODE = 0 VBUS > UVLO or HZ_MODE = 0, OPA_MODE = 1 V(AUXPWR) > V(LOWV) or V(AUXPWR) + V(SHORT) or OTG Active                                                                                    | OPA_MODE = 0 OTG Inactive or HZ_MODE = 1 or V <sub>(AUXPWR)</sub> > V <sub>(LOWV)</sub> Boost Start Up Finished                | OPA_MODE = 0 OTG Inactive or HZ_MODE = 1 or V <sub>(AUXPWR)</sub> > V <sub>(BAT)</sub> MIN or Faults                 |

|               | On                                                                                                                                                                                                              | On                                                                                                                             | On                                                                                                                   |

|               | Off                                                                                                                                                                                                             | Off                                                                                                                            | Off                                                                                                                  |

|               | Off                                                                                                                                                                                                             | Off                                                                                                                            | Off                                                                                                                  |

|               | Off                                                                                                                                                                                                             | Off                                                                                                                            | On                                                                                                                   |

|               | Off                                                                                                                                                                                                             | On/Off <sup>(1)</sup>                                                                                                          | On                                                                                                                   |

#### (1) Q1 is OFF when VBUS is shorted to ground.

Figure 26. State Diagram for bq24152

#### SERIAL INTERFACE DESCRIPTION

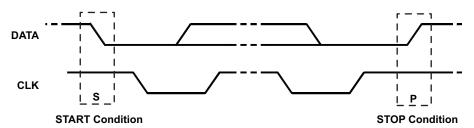

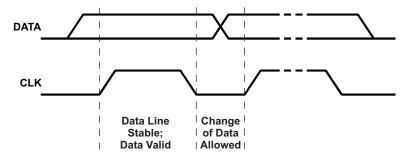

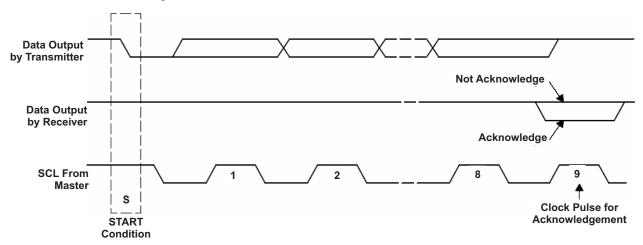

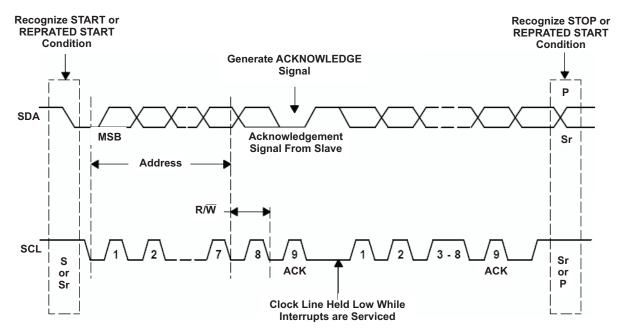

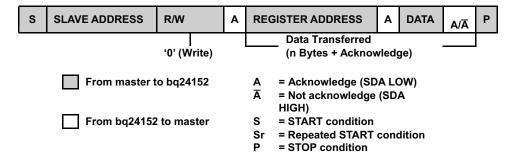

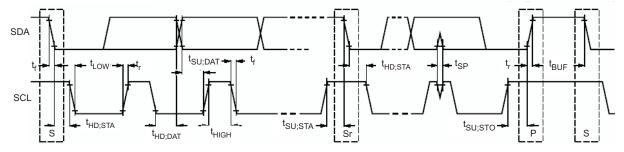

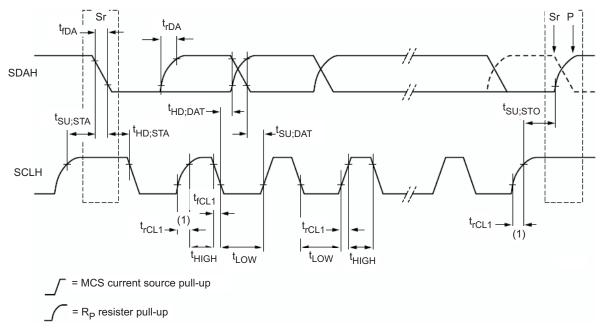

I<sup>2</sup>C™ is a 2-wire serial interface developed by Philips Semiconductor (see I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000). The bus consists of a data line (SDA) and a clock line (SCL) with pull-up structures. When the bus is idle, both SDA and SCL lines are pulled high. All the I<sup>2</sup>C compatible devices connect to the I<sup>2</sup>C bus through open drain I/O pins, SDA and SCL. A master device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A slave device receives and/or transmits data on the bus under control of the master device.

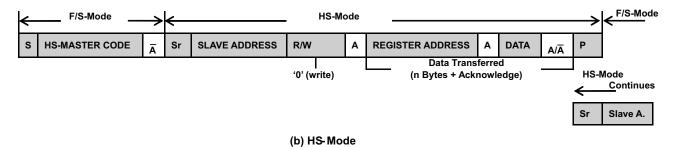

The bq24152 device works as a slave and supports the following data transfer modes, as defined in the  $I^2C$ -Bus<sup>TM</sup> Specification: standard mode (100 kbps), fast mode (400 kbps), and high-speed mode (up to 3.4 Mbps in write mode). The interface adds flexibility to the battery charge solution, enabling most functions to be programmed to new values depending on the instantaneous application requirements. Register contents remain intact as long as supply voltage remains above 2.2 V (typical).

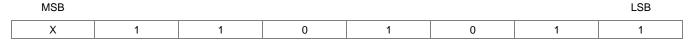

The data transfer protocol for standard and fast modes is exactly the same; therefore, they are referred to as the F/S-mode in this document. The protocol for high-speed mode is different from the F/S-mode, and it is referred to as the HS-mode. The bq24152 device only supports 7-bit addressing. The device 7-bit address is defined as '1101011' (6BH).

#### **F/S Mode Protocol**

The master initiates data transfer by generating a start condition. The start condition is when a high-to-low transition occurs on the SDA line while SCL is high, as shown in Figure 27. All I<sup>2</sup>C-compatible devices should recognize a start condition.

Figure 27. START and STOP Condition