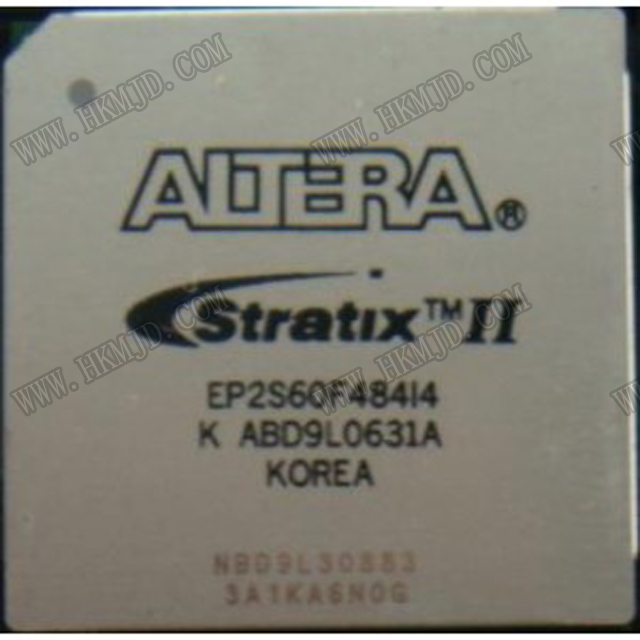

EP2S60F484I4 Datasheet (PDF) - Altera Corporation

| 型号 | 品牌 | 批号 | 封装 | 数量 | 备注 | 资料 |

| EP2C8F256CXNAA | ALTERA | 13+ | BGA-256 | 98565 | 100% brand new and original(100%全新原装) |

|

| EP2SGX90EF1152C4ES | ALTERA | 20+ | BGA | 1057 | 全新原装New and original have in stock |

|

| EP2SGX130GF1508C3N | ALTERA | 1137+ | BGA | 10 | 原装现货original spot stock |

|

| EP2SGX130GF1508C4 | Altera | 13+ | BGA | 57680 | 100%全新原装 Original |

|

| EP2AGX45DF25C6N | Altera | 13+ | Standard | 57680 | 100%全新原装 Original |

|

| EP2AGX95EF29I5N | Altera | 13+ | BGA | 57680 | 100%全新原装 Original |

|

| EP2AGX125EF29I5N | ALTERA | 09+ | BGA780 | 100 | 原装现货original spot stock |

|

| EP2C20F484I8N | Altera | 13+ | Standard | 45870 | Original 进口原装现货 |

|